超前进位加法器设计报告分解,超前进位加法器设计实验

本作品内容为超前进位加法器设计报告分解,格式为 doc ,大小 318466 KB ,页数为 16页

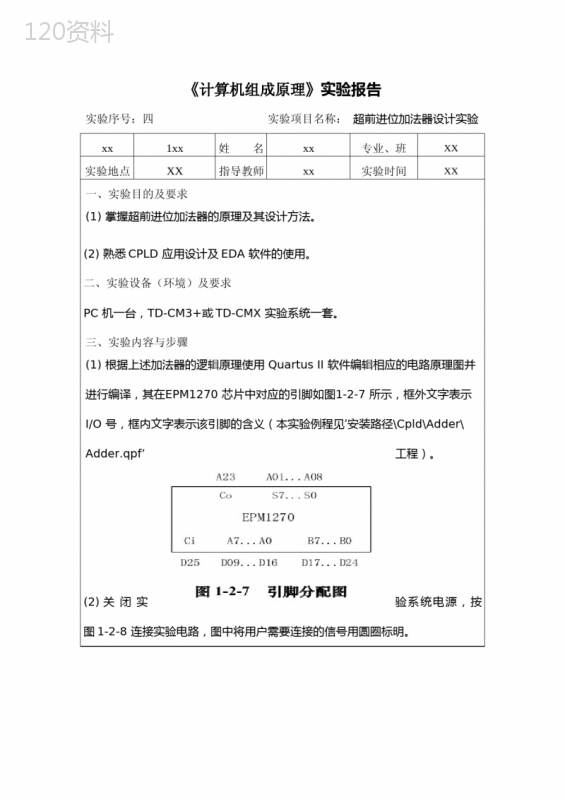

('华东交大理工学院课程设计存档资料成绩:华东交通大学理工学院课程设计报告书所属课程名称EDA课程设计题目超前进位加法器设计分院专业班级学号学生姓名指导教师2013年7月2日第1页共16页华东交大理工学院课程设计目录第一章设计内容与要求..................................................................3第二章超前进位加法器设计原理....................................................4第三章详细设计流程....................................................................53.1.创建工程文件...................................................................53.2.程序的编译......................................................................63.3.波形的仿真......................................................................8第四章设计结果分析..................................................................12第五章源程序代码.....................................................................13第六章心得体会........................................................................15第七章参考文献........................................................................16第2页共16页华东交大理工学院课程设计第一章设计内容与要求加法运算是最重要也是最基本的运算,所有的其他基本运算,如减、乘、除运算最终都能归结为加法运算。但因为加法运算存在进位问题,使得某一位计算结果的得出和所有低于他的位相关。因此为了减少进位传输所消耗的时间,提高计算速度,人们设计了多种类型的加法器,如跳跃进位加法器、进位选择加法器、超前进位加法器等。本设计采用的是超前进位加法器。通过Verilog设计一个超前8位加法器。要求在QuartusII软件下,利用Verilog编程完成层次式电路设计,电路中的元件可以用Verilog设计也可以用库元件连线构成再封装。8位超前进位加法器,借助EDA工具中的综合器,适配器,时序仿真器和编程器等工具进行相应处理。适配采用Cyclone系列的EP1C6Q240C8。要求综合出RTL电路,并进行仿真输入波形设计并分析电路输出波形.试比较并阐述数据类型reg型和wire型的区别。第二章超前进位加法器设计原理将n个全加器相连可得n位加法器,但是加法时间较长。解决的方法之一是采用“超前进位产生电路”来同时形成各位进位,从而实现快速加法。超前进位产生电路是根据各位进位的形成条件来实现的首先对于1位加法器基本位值和与进位输出为1;如果a,b有一个为1,则进位输出等于cin;令G=ab,P=a+b,则有:Cout==ab+(a+b)cin=G+P•cin由此可以G和P来写出4位超前进位链如下(设定四位被加数和加数为A第3页共16页华东交大理工学院课程设计和B,进位输入Cin,进位输出为cout,进位产生Gi=AiBi,进位传输Pi=Ai+Bi);C0=cin;C1=G0+P0C0=G0+P0•cinC2=G1+P1C1=G1+P1(G0+P0cin)=G1+P1G0+P1P0cinC3=G2+P2C2=G2+P2(G1+P1cin)=G2+P2G1+P2P1G0+P2P1P0cinC4=G3+P3C3=G3+P3(G2+P2C2)=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0cinCout=c4由超前进位链,各个进位彼此独立产生,将进位级联传播给去掉了,因此,减小了进位产生的延迟时间。同样可推导出下面的式子:SUM=A⊕B⊕Cin=(AB)⊕(A+B)⊕CinU=G⊕P⊕Cin本实验中采用8位超前进位加法器第三章详细设计流程3.1.创建工程文件打开QuartusII9.1创建一个工程文件adder_ahead选择菜单File中NewProjectWizard命令,在如下“工程设置”对话框中单击右侧“…”按钮,找到文件夹D:\\atlera\\quartus,选中已存盘的add_ahead.vhd的文件。第4页共16页华东交大理工学院课程设计单击Next,将与工程有关的文件加入此工程。(1)选择仿真器和综合器类型。都选默认的None。(2)选择目标芯片。(3)工具设置。这里默认使用QuartusⅡ自含的所有设计工具。(4)结束设置。3.2.程序的编译(1).选择菜单“Processing”—“StartCompilation”命令,或者点击运行编译按钮,启动完全编译,这里的完全编译包括分析与综合、适配装配文件、定时分析、网编文件提取过程。如果只要进行期中的某一项编译,可以选着“Tools”---“CompilerTool”命令,或者点击按钮即可出现编译工具选择串口,共包括5个编译工具,分别为分析与综合器、适配器、装配器、定时分析器、网表文件提提取器,单机每个工具前面的小图标可单独启动每一个编译器。第5页共16页华东交大理工学院课程设计(2)编译完成后,会将有关的编译信息显示在窗口中,可查看其中的相关内容。还可以查看中和后的电路原理图,选择“Tools”---“NetlistViewers”---“RTLViewer”菜单命令,既可观察综合生成的RLT方式的电路原理图,在这里我们可以看到8位超期进位加法器生成的原理图第6页共16页华东交大理工学院课程设计如下:8位超期进位加法器生成的原理图:第7页共16页华东交大理工学院课程设计3.3.波形的仿真仿真时序,对项目进行仿真测试,也可以对项目中的某一个子模块进行仿真,其方法是选择菜单“Assignment”---“Wizard”----“SimulatorSetWizard”命令,在设置过程中指定仿真对象,并指定对象的仿真类型、矢量激励源等。(1)打开波形编辑器选择菜单“File”---“New”命令,在“New”对话框中选择“OtherFile”页中的“VectorWaveFile”选项,单击“ok”按钮,即出现选择波形按钮;(2)输入信号节点第8页共16页华东交大理工学院课程设计选择菜单“View”---“UtilityWindows”---“NodeFinder”命令,出现对话框,在“Filter”下拉列表中选择“Pins:all”选项,再次单击“List”按钮,即在下面的“NodesFound”框中出现本设计项目的所有端口引脚列表,从端口列表中选择所需要的,并逐个拖到波形编辑窗口中(4)编辑输入信号波形点击波形编辑窗口中的全屏显示,使用波形编辑窗口中的各种波形赋值,编辑各输入信号的激励波形。在仿真的时候需要设置一个合理的区域,选择菜单“Edit”---“EndTime”命令,在淡出的“Time”窗口中输入60us.第9页共16页华东交大理工学院课程设计对数据的型号的格式可以选择:Binary(二进制),Hexadecimal(十六进制)、Octal(八进制)、SignedDecimal(有符号十进制),UnsgnedDecimal(无符号十进制)。这里选择的是Binary二进制,便于观察结果。第10页共16页华东交大理工学院课程设计(5)仿真参数的设置,选择菜单“Assignments”—“Setting”命令,在弹出的对话框选择“SimulatorSetting”项下的“Mode”,以选择仿真模式,仿真模式有功能仿真模式和时序仿真模式,这里选择功能仿真。(6)观察仿真结果选择菜单“Processing”---“StartSimulation”命令,即启动仿真器工作。仿真完毕后,可以通过输出波形,检验所设计电路的功能是否正确8位超前进位的功能输出波形图:第11页共16页华东交大理工学院课程设计第四章设计结果分析输入a0010011000100111输入b00101011001010111cin0101sum01101000011010010110101001101011结果中显示是正常的,8位超前进位加法器得到成功的实现8位超前进位器综合后的RTL级原理图第12页共16页华东交大理工学院课程设计第五章源程序代码8位超前进位加法器moduleadd_ahead(sum,cout,a,b,cin);input[7:0]a,b;inputcin;output[7:0]sum;outputcout;wire[7:0]G,P;wire[7:0]C,sum;assignG[0]=a[0]&b[0];assignP[0]=a[0]b[0];assignC[0]=cin;assignsum[0]=G[0]^P[0]^C[0];assignG[1]=a[1]&b[1];assignP[1]=a[1]b[1];assignC[1]=G[0](P[0]&cin);assignsum[1]=G[1]^P[1]^C[1];第13页共16页华东交大理工学院课程设计assignP[2]=a[2]&b[2];assignC[2]=G[1](P[1]&C[1]);assignsum[2]=G[2]^P[2]^C[2];assignG[3]=a[3]&b[3];assignP[3]=a[3]b[3];assignC[3]=G[2](P[2]&C[2]);assignsum[3]=G[3]^P[3]^C[3];assignG[4]=a[4]&b[4];assignP[4]=a[4]b[4];assignC[4]=G[3](P[3]&C[3]);assignsum[4]=G[2]^P[2]^C[2];assignG[5]=a[5]&b[5];assignP[5]=a[5]b[5];assignC[5]=G[4](P[4]&C[4]);assignsum[5]=G[5]^P[5]^C[5];assignG[6]=a[6]&b[6];assignP[6]=a[6]b[6];assignC[6]=G[5](P[5]&C[5]);assignsum[6]=G[6]^P[6]^C[6];assignG[7]=a[7]&b[7];assignP[7]=a[7]b[7];assignC[7]=G[6](P[6]&C[6]);assignsum[7]=G[7]^P[7]^C[7];assigncout=G[7](P[7]&C[7]);endmodule第14页共16页华东交大理工学院课程设计第六章心得体会本学期学习了EDA技术与Vertlog技术,对EDA技术应用有了一些了解,在如今生活在这个数字化和信息化时代,数字产品的广泛应用越来越多。EDA技术的使用在我们生活中息息相关,发现了EDA的强大功能。系统系设计,混合电路设计,综合仿真的设计,数字电路设计,版图设计,PCB板设计,PLD开发,高速电路设计,模拟电路设计等应用。这次课设中用到的QuartusⅡ软件,在安装过程中遇到不能仿真,后来下载了9.11版本得到解决。QuartusⅡ进行EDA开发包括设计输入,编译,仿真,编程和验证,自己通过设计8位超前加法器对QuartusⅡ软件的应用也得到了一定的掌握。在编译的过程中遇到一些不能编译,通过网上找资料和同学的讨论得到了一定的了解,通过软件的设置和通过编译错误的提示来更改错误,对设计的原理有了更深的理解。同时也发现遇到问题不要急着马上就向同学寻求帮助,我们自己可以认真地独立思考,想想问题哪里出错了,这样自己才会有不断地提高。认识涞源于实践实践是用于检验真理的唯一标准。这次使用超前进位这样就减少了延时,加快了运行速度。对于一切的设计我们都要多思考,使用最优的方法到我们实际生活当中去。这次课设设计,加强了我们自己动手,思考解决问题的能力。也让我们在学习的道路求知的一段探索道路,是对于我们生活一种充实。第15页共16页华东交大理工学院课程设计第七章参考文献(1)《EDA技术与Verilog设计》科学出版社王金明(2)《数字电子技术基础》,高等教育出版社阎石(3)《专用集成电路》,电子工业出版社第16页共16页',)

提供超前进位加法器设计报告分解,超前进位加法器设计实验会员下载,编号:1700819667,格式为 docx,文件大小为16页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载