超前进位加法器设计实验实验,超前进位加法器实验心得

本作品内容为超前进位加法器设计实验实验,格式为 doc ,大小 76288 KB ,页数为 4页

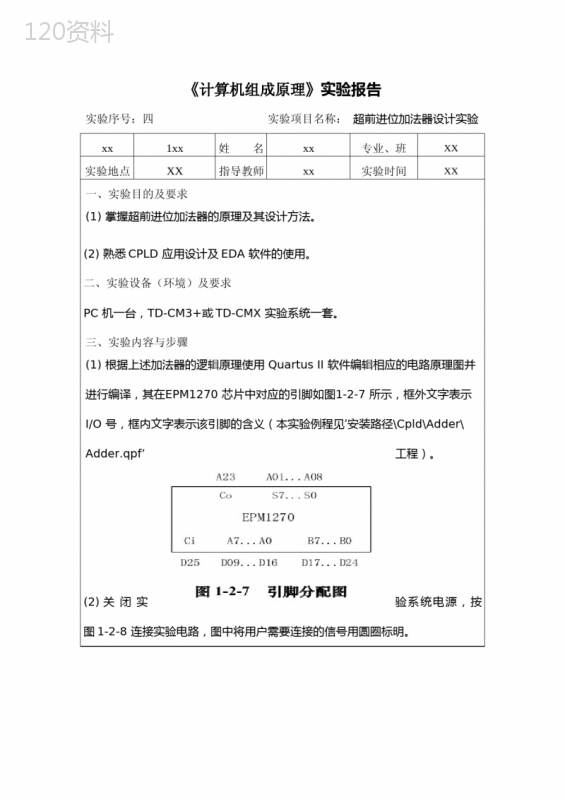

('《计算机组成原理》实验报告实验序号:四实验项目名称:超前进位加法器设计实验xx1xx姓名xx专业、班XX实验地点XX指导教师xx实验时间XX一、实验目的及要求(1)掌握超前进位加法器的原理及其设计方法。(2)熟悉CPLD应用设计及EDA软件的使用。二、实验设备(环境)及要求PC机一台,TD-CM3+或TD-CMX实验系统一套。三、实验内容与步骤(1)根据上述加法器的逻辑原理使用QuartusII软件编辑相应的电路原理图并进行编译,其在EPM1270芯片中对应的引脚如图1-2-7所示,框外文字表示I/O号,框内文字表示该引脚的含义(本实验例程见‘安装路径\\Cpld\\Adder\\Adder.qpf’工程)。(2)关闭实验系统电源,按图1-2-8连接实验电路,图中将用户需要连接的信号用圆圈标明。(3)打开实验系统电源,将生成的POF文件下载到EPM1270中去。(4)以CON单元中的SD17…SD10八个二进制开关为被加数A,SD07…SD00八个二进制开关为加数B,K7用来模拟来自低位的进位信号,相加的结果在CPLD单元的L7…L0八个LED灯显示,相加后向高位的进位用CPLD单元的L8灯显示。给A和B置不同的数,观察相加的结果。四、实验结果与数据处理如在SD17...SD10中输入11111001,在SD07...SD00中输入10011111,在实验箱中可看到用来模拟低位与高位的进位信号K7、L8灯变亮,同时可看到A01...A08与L7...L0上的显示分别为1001与1000。五、分析与讨论(心得)这个实验是上个实验的扩展,进一步加深了我对运算器的认识。现实生活中我们也要学会对已有的知识的一种扩展补充,进一步加深对已有知识的巩固,并探索其更深层次的东西,设计出与众不同的东西来。这个算法的核心是把8位加法器分成两个4位加法器,先求出低4位加法器的各个进位,特别是向高4位加法器的进位C4。然后,高4位加法器把C4作为初始进位,使用低4位加法器相同的方法来完成计算。每一个4位加法器在计算时,又分成了两个2位的加法器。如此递归。随着加法器位数的增加,越是高位的进位逻辑电路就会越复杂:定义Gi,j=gi+pigi-1+pipi-1gi-2+…+pipi-1…pj+1gj;Pi,j=pipi-1…pj+1pj则有Gi,i=gi;Pi,i=pi;Gi,j=Gi,k+Pi,kGk-1,j;Pi,j=Pi,kPk-1,jCi+1=Gi,j+Pi,jCj从而可知四位超前进位加法算法如下:G1,0=g1+p1g0;P1,0=p1p0G3,2=g3+p3g2;P3,2=p3p2G3,0=G3,2+P3,2G1,0;P3,0=P3,2P1,0C4=G3,0+P3,0C0八位超前进位加法算法如下:G1,0=g1+p1g0;P1,0=p1p0G3,2=g3+p3g2;P3,2=p3p2G3,0=G3,2+P3,2G1,0;P3,0=P3,2P1,0G5,4=g5+p5g4;P5,4=p5p4G7,6=g7+p7g6;P7,6=p7p6G7,4=G7,6+P7,6G5,4;P7,4=P7,6P5,4G7,0=G7,4+P7,4G3,0;P7,0=P7,4P3,0C8=G7,0+P7,0C0六、教师评语签名:日期:成绩',)

提供超前进位加法器设计实验实验,超前进位加法器实验心得会员下载,编号:1700819667,格式为 docx,文件大小为4页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载