杭电计组实验2-超前进位加法器设计实验

本作品内容为杭电计组实验2-超前进位加法器设计实验,格式为 doc ,大小 106024 KB ,页数为 6页

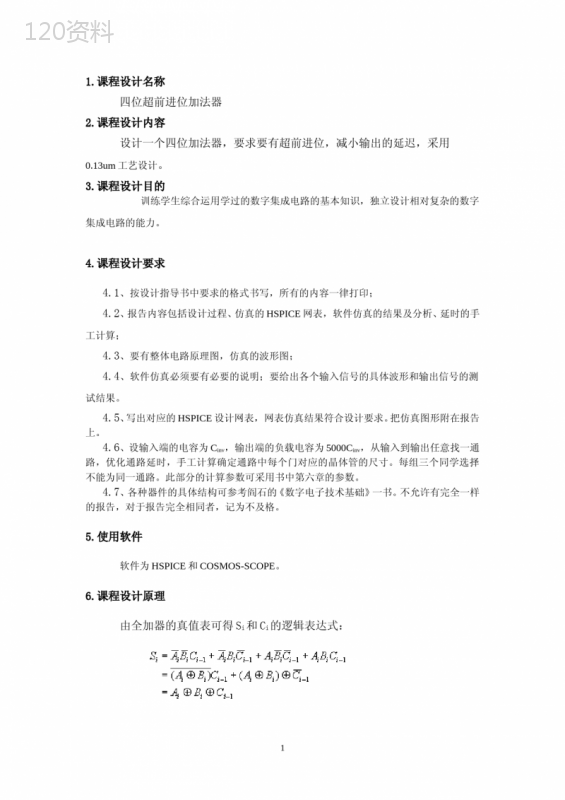

('杭州电子科技大学计算机学院实验报告实验项目:实验2-超前进位加法器设计实验课程名称:计算机组成原理与系统结构课程设计姓名:学号:同组姓名:学号:实验位置(机号):实验日期:指导教师:实验内容(算法、程序、步骤和方法)一、实验目的(1)掌握运用VerilogHDL进行数据流描述与建模的技巧和方法,掌握模块调用与实例引用的方法。(2)掌握超前进位加法器的原理和设计方法二、实验仪器ISE工具软件三、步骤、方法(1)启动XilinxISE软件,选择File->NewProject,输入工程名shiyan2,默认选择后,点击Next按钮,确认工程信息后点击Finish按钮,创建一个完整的工程。(2)在工程管理区的任意位置右击,选择NewSource命令。弹出NewSourceWizard对话框,选择VerilogModule,并输入Verilog文件名,点击Next按钮进入下一步,点击Finish完成创建。(3)编辑程序源代码,然后编译,综合;选择Synthesize--XST项中的CheckSyntax右击选择Run命令,并查看RTL视图;如果编译出错,则需要修改程序代码,直至正确。(4)在工程管理区将View类型设置成Simulation,在任意位置右击,选择NewSource命令,选择VerilogTestFixture选项。点击Next,点击Finish,完成。编写激励代码,观察仿真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。(5)由于实验二并未链接实验板,所以后面的链接实验板的步骤此处没有。操作过程及结果一,操作过程实验过程和描述:moduleshiyan2(A,B,C0,C4,F);input[3:0]A,B;inputC0;output[3:0]F;outputC4;wire[3:0]A,B,F;wireC0,C4;assignG0=A[0]&B[0];assignG1=A[1]&B[1];assignG2=A[2]&B[2];assignG3=A[3]&B[3];assignP0=A[0]B[0];assignP1=A[1]B[1];assignP2=A[2]B[2];assignP3=A[3]B[3];assignC1=G0(P0&C0);assignC2=G1(P1&C1);assignC3=G2(P2&C2);assignC4=G3(P3&C3);assignF[0]=A[0]^B[0]^C0;assignF[1]=A[1]^B[1]^C1;assignF[2]=A[2]^B[2]^C2;assignF[3]=A[3]^B[3]^C3;Endmodule仿真代码moduleshiyan2_test;//Inputsreg[3:0]A;reg[3:0]B;regC0;//OutputswireC4;wire[3:0]F;//InstantiatetheUnitUnderTest(UUT)shiyan2uut(.A(A),.B(B),.C0(C0),.C4(C4),.F(F));initialbegin//InitializeInputsA=0;B=0;C0=0;//Wait100nsforglobalresettofinish#100;//AddstimulushereA=1100;B=1011;C0=0;#100;A=1011;B=0010;C0=1;#100;A=1011;B=1101;C0=0;#100;A=1010;B=0010;C0=1;#100;A=0111;B=1000;C0=0;#100;A=0011;B=0100;C0=1;#100;A=1001;B=0001;C0=0;#100;endEndmoduleRTL图二、结果思考题:(1)综合得到的电路图,它和想要设计的电路在引脚的输入输出方面是完全相同的,但是相比较内部的RTL图,实验实现的结果是相同的,但是我编写的实验代码并没有调用实验一的全加器设计。(2)尝试编写8位超前进位加法器设计实验moduleadd_8(input[7:0]a,input[7:0]b,inputcin,output[7:0]s,outputco);wire[7:0]c_tmp;wire[7:0]g;wire[7:0]p;assignco=c_tmp[7];assigng[0]=a[0]&b[0],g[1]=a[1]&b[1],g[2]=a[2]&b[2],g[3]=a[3]&b[3],g[4]=a[4]&b[4],g[5]=a[5]&b[5],g[6]=a[6]&b[6],g[7]=a[7]&b[7];assignp[0]=a[0]b[0],p[1]=a[1]b[1],p[2]=a[2]b[2],p[3]=a[3]b[3],p[4]=a[4]b[4],p[5]=a[5]b[5],p[6]=a[6]b[6],p[7]=a[7]b[7];assignc_tmp[0]=g[0](p[0]&cin),c_tmp[1]=g[1](p[1]&g[0])(p[1]&p[0]&cin),c_tmp[2]=g[2](p[2]&g[1])(p[2]&p[1]&g[0])(p[2]&p[1]&p[0]&cin),c_tmp[3]=g[3](p[3]&g[2])(p[3]&p[2]&g[1])(p[3]&p[2]&p[1]&g[0])(p[3]&p[2]&p[1]&p[0]&cin),c_tmp[4]=g[4](p[4]&g[3])(p[4]&p[3]&g[2])(p[4]&p[3]&p[2]&g[1])(p[4]&p[3]&p[2]&p[1]&g[0])(p[4]&p[3]&p[2]&p[1]&p[0]&cin),c_tmp[5]=g[5](p[5]&g[4])(p[5]&p[4]&g[3])(p[5]&p[4]&p[3]&g[2])(p[5]&p[4]&p[3]&p[2]&g[1])(p[5]&p[4]&p[3]&p[2]&p[1]&g[0])(p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&cin),c_tmp[6]=g[6](p[6]&g[5])(p[6]&p[5]&g[4])(p[6]&p[5]&p[4]&g[3])(p[6]&p[5]&p[4]&p[3]&g[2])(p[6]&p[5]&p[4]&p[3]&p[2]&g[1])(p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&g[0])(p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&cin),c_tmp[7]=g[7](p[7]&g[6])(p[7]&p[6]&g[5])(p[7]&p[6]&p[5])(p[7]&p[6]p[5]&p[4]&g[3])(p[7]&p[6]&p[5]&p[4]&p[3]&g[2])(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&g[1])(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&g[0])(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&cin);assigns[7:0]=a[7:0]^b[7:0]^{c_tmp[6:0],cin};endmodule(3)在这个试验中对于F的输出,编写遇到了阻碍,后来仔细阅读了实验二的实验要求和实验内容,F是A和B的算数和。由于F是四位的输出,所以便有了assignF[0]=A[0]^B[0]^C0;assignF[1]=A[1]^B[1]^C1;assignF[2]=A[2]^B[2]^C2;assignF[3]=A[3]^B[3]^C3;整个过程中也再没遇到其他的问题,实验二又运行结束。实验体会在这个超前进位加法器设计实验中,这个实验理解起来稍微有点困难,费了很大的功夫功夫。在理解F这个四位的输出时,有点不太懂,最后所幸的是解决了。通过做这个超前进位加法器设计实验,我对数据流的描述方式有了一个全新的理解。也对ISE这个软件的运用更加熟练了,对超前进位加法器这个概念也有了更深层次的理解,增长了我的知识,强化了我的实践能力以及思考能力。这次实验收获很大。指导教师评议实验步骤写的时候,最好自己按照所做步骤写,二人不要一模一样。成绩:指导教师签名:',)

提供杭电计组实验2-超前进位加法器设计实验会员下载,编号:1700819385,格式为 docx,文件大小为6页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载