2006031459-黄德荣-5位逐级进位和超前进位加法器设计

本作品内容为2006031459-黄德荣-5位逐级进位和超前进位加法器设计,格式为 doc ,大小 71168 KB ,页数为 9页

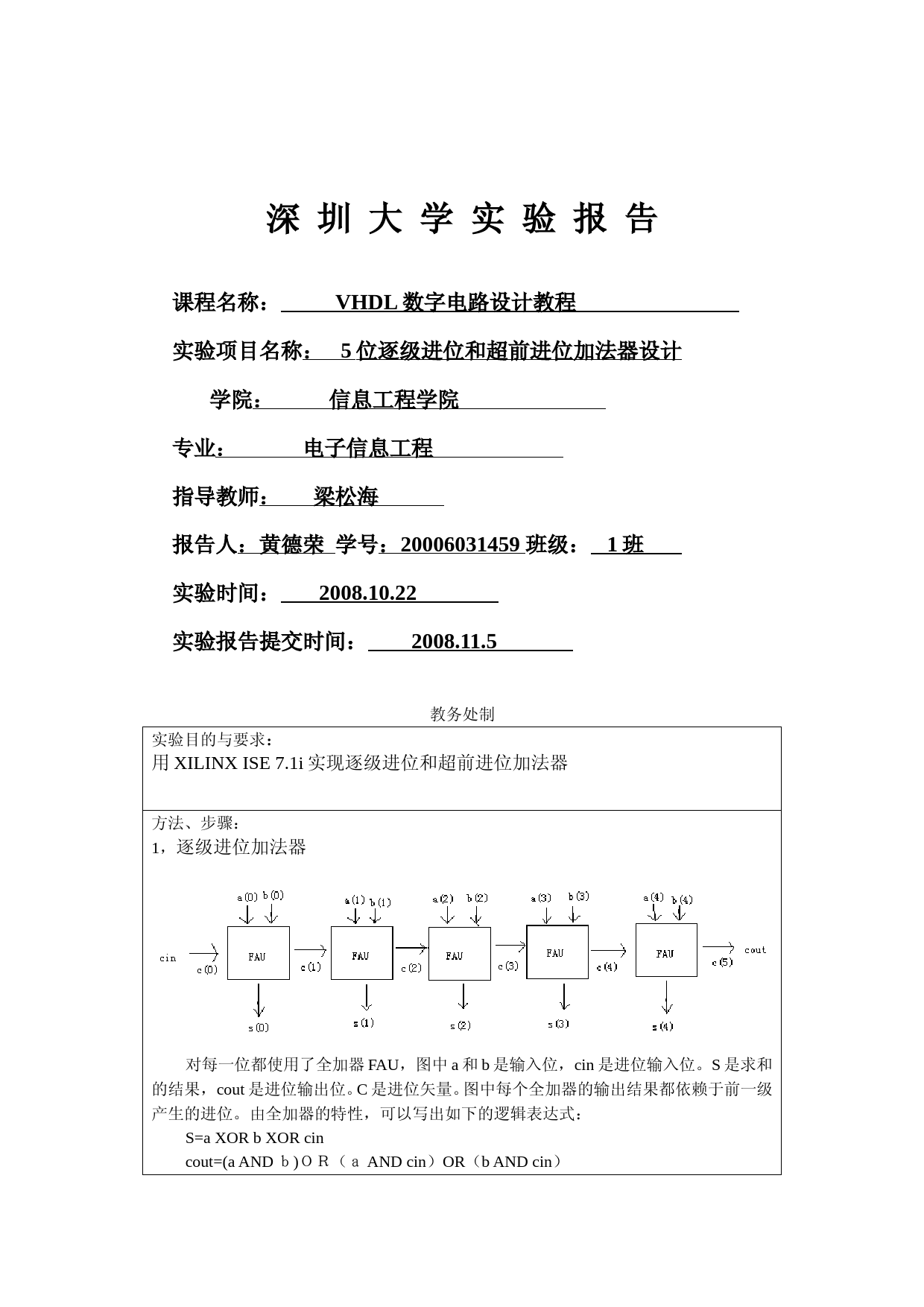

('深圳大学实验报告课程名称:VHDL数字电路设计教程实验项目名称:5位逐级进位和超前进位加法器设计学院:信息工程学院专业:电子信息工程指导教师:梁松海报告人:黄德荣学号:20006031459班级:1班实验时间:2008.10.22实验报告提交时间:2008.11.5教务处制实验目的与要求:用XILINXISE7.1i实现逐级进位和超前进位加法器方法、步骤:1,逐级进位加法器对每一位都使用了全加器FAU,图中a和b是输入位,cin是进位输入位。S是求和的结果,cout是进位输出位。C是进位矢量。图中每个全加器的输出结果都依赖于前一级产生的进位。由全加器的特性,可以写出如下的逻辑表达式:S=aXORbXORcincout=(aANDb)OR(aANDcin)OR(bANDcin)2,超前进位加法器电路实现是需要两个非常重要的中间信号:generate和propagate,分别由g和p表示。加法器两个输入位是a和b,则generate和propagate信号定义如下:g=aANDbp=aXORb这两个信号与进位无关,只根据当前的输入计算。现在两个输入矢量是:a=a(4)a(3)a(2)a(1)a(0)和b=b(4)b(3)b(2)b(1)b(0),那么相应的generate矢量为g=g(4)g(3)g(2)g(1)g(0),相应的propagate矢量为p=p(4)p(3)p(2)p(1)p(0)。其中:g(j)=a(j)ANDb(j)p(j)=a(j)XORb(j)同时,进位矢量用c=c(4)c(3)c(2)c(1)c(0)。进位可由g和p按照下面的方法计算得到:c(0)=cin;c(1)=c(0)p(0))+g(0);c(2)=c(0)p(0)p(1))+g(0)p(1)+g(1);c(3)=c(0)p(0)p(1)p(2)+g(0)p(1)p(2)+(g(1)p(2)+g(2);c(4)=c(0)p(0)p(1)p(2)p(3)+g(0)p(1)p(2)p(3)+g(1)p(2)p(3)+g(2)p(3)+g(3);c(5)=c(0)p(0)p(1)p(2)p(3)p(4)+g(0)p(1)p(2)p(3)p(4)+g(1)p(2)p(3)p(4)+g(2)p(3)p(4)+g(4);可见超前进位加法器的每个全加器不依赖与前一级进位输出的计算结果,有利于提高电路执行速度。实验过程及内容:1,逐级进位加法器VHDL代码----------------------------------------------------------------------------------Company:--Engineer:----CreateDate:02:59:1810/22/08--DesignName:--ModuleName:adder-Behavioral--ProjectName:--TargetDevice:--Toolversions:--Description:----Dependencies:----Revision:--Revision0.01-FileCreated--AdditionalComments:----------------------------------------------------------------------------------libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;useIEEE.STD_LOGIC_ARITH.ALL;useIEEE.STD_LOGIC_UNSIGNED.ALL;----Uncommentthefollowinglibrarydeclarationifinstantiating----anyXilinxprimitivesinthiscode.--libraryUNISIM;--useUNISIM.VComponents.all;entityadderisport(a,b:instd_logic_vector(4downto0);cin:instd_logic;s:outstd_logic_vector(4downto0);cout:outstd_logic);endadder;architectureBehavioralofadderissignalc:std_logic_vector(4downto0);beginc(0)<=cin;s(0)<=a(0)xorb(0)xorc(0);c(1)<=(a(0)andb(0))or(a(0)andc(0))or(b(0)andc(0));s(1)<=a(1)xorb(1)xorc(1);c(2)<=(a(1)andb(1))or(a(1)andc(1))or(b(1)andc(1));s(2)<=a(2)xorb(2)xorc(2);c(3)<=(a(2)andb(2))or(a(2)andc(2))or(b(2)andc(2));s(3)<=a(3)xorb(3)xorc(3);c(4)<=(a(3)andb(3))or(a(3)andc(3))or(b(3)andc(3));s(4)<=a(4)xorb(4)xorc(4);cout<=(a(4)andb(4))or(a(4)andc(4))or(b(4)andc(4));endBehavioral;仿真波形2,超前进位加法器VHDL代码----------------------------------------------------------------------------------Company:--Engineer:----CreateDate:14:51:1411/05/08--DesignName:--ModuleName:sd-Behavioral--ProjectName:--TargetDevice:--Toolversions:--Description:----Dependencies:----Revision:--Revision0.01-FileCreated--AdditionalComments:----------------------------------------------------------------------------------libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;useIEEE.STD_LOGIC_ARITH.ALL;useIEEE.STD_LOGIC_UNSIGNED.ALL;----Uncommentthefollowinglibrarydeclarationifinstantiating----anyXilinxprimitivesinthiscode.--libraryUNISIM;--useUNISIM.VComponents.all;entitysdisport(a,b:instd_logic_vector(4downto0);cin:instd_logic;s:outstd_logic_vector(4downto0);cout:outstd_logic);endsd;architectureBehavioralofsdissignalc:std_logic_vector(5downto0);signalp:std_logic_vector(4downto0);signalg:std_logic_vector(4downto0);beginp(0)<=a(0)xorb(0);g(0)<=a(0)andb(0);c(0)<=cin;s(0)<=p(0)xorc(0);p(1)<=a(1)xorb(1);g(1)<=a(1)andb(1);c(1)<=(cinandp(0))org(0);s(1)<=p(1)xorc(1);p(2)<=a(2)xorb(2);g(2)<=a(2)andb(2);c(2)<=(cinandp(0)andp(1))or(g(0)andp(1))org(1);s(2)<=p(2)xorc(2);p(3)<=a(3)xorb(3);g(3)<=a(3)andb(3);c(3)<=(cinandp(0)andp(1)andp(2))or(g(0)andp(1)andp(2))or(g(1)andp(2))org(2);s(3)<=p(3)xorc(3);p(4)<=a(4)xorb(4);g(4)<=a(4)andb(4);c(4)<=(cinandp(0)andp(1)andp(2)andp(3))or(g(0)andp(1)andp(2)andp(3))or(g(1)andp(2)andp(3))or(g(2)andp(3))org(3);s(4)<=p(4)xorc(4);c(5)<=(cinandp(0)andp(1)andp(2)andp(3)andp(4))or(g(0)andp(1)andp(2)andp(3)andp(4))or(g(1)andp(2)andp(3)andp(4))or(g(2)andg(3)andp(4))or(g(3)andp(4))org(4);cout<=c(5);endBehavioral;仿真波形实验结论:通过实验基本上掌握了VHDL的语法,同时对逐级进位和超前进位加法器的工作原理有了深入的了解。指导教师批阅意见:成绩评定:指导教师签字:年月日备注:注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。',)

提供2006031459-黄德荣-5位逐级进位和超前进位加法器设计会员下载,编号:1700818634,格式为 docx,文件大小为9页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。