UART,uart

本作品内容为UART,格式为 doc ,大小 130048 KB ,页数为 3页

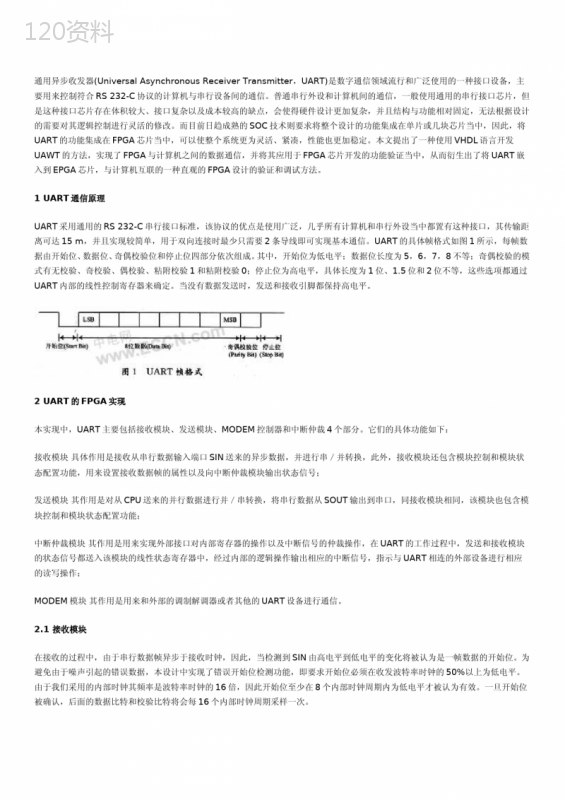

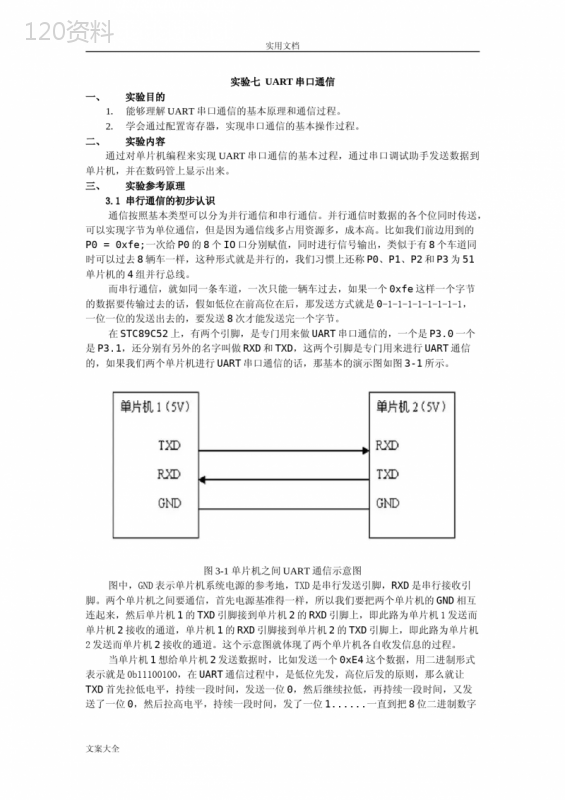

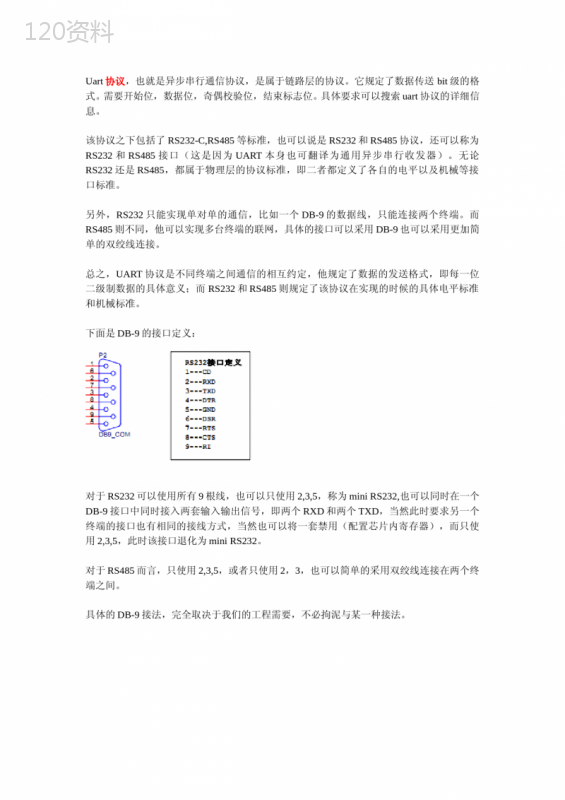

('通用异步收发器(UniversalAsynchronousReceiverTransmitter,UART)是数字通信领域流行和广泛使用的一种接口设备,主要用来控制符合RS232-C协议的计算机与串行设备间的通信。普通串行外设和计算机间的通信,一般使用通用的串行接口芯片,但是这种接口芯片存在体积较大、接口复杂以及成本较高的缺点,会使得硬件设计更加复杂,并且结构与功能相对固定,无法根据设计的需要对其逻辑控制进行灵活的修改。而目前日趋成熟的SOC技术则要求将整个设计的功能集成在单片或几块芯片当中,因此,将UART的功能集成在FPGA芯片当中,可以使整个系统更为灵活、紧凑,性能也更加稳定。本文提出了一种使用VHDL语言开发UAWT的方法,实现了FPGA与计算机之间的数据通信,并将其应用于FPGA芯片开发的功能验证当中,从而衍生出了将UART嵌入到EPGA芯片,与计算机互联的一种直观的FPGA设计的验证和调试方法。1UART通信原理UART采用通用的RS232-C串行接口标准,该协议的优点是使用广泛,几乎所有计算机和串行外设当中都置有这种接口,其传输距离可达15m,并且实现较简单,用于双向连接时最少只需要2条导线即可实现基本通信。UART的具体帧格式如图1所示,每帧数据由开始位、数据位、奇偶校验位和停止位四部分依次组成。其中,开始位为低电平;数据位长度为5,6,7,8不等;奇偶校验的模式有无校验、奇校验、偶校验、粘附校验1和粘附校验0;停止位为高电平,具体长度为1位、1.5位和2位不等,这些选项都通过UART内部的线性控制寄存器来确定。当没有数据发送时,发送和接收引脚都保持高电平。2UART的FPGA实现本实现中,UART主要包括接收模块、发送模块、MODEM控制器和中断仲裁4个部分。它们的具体功能如下:接收模块具体作用是接收从串行数据输入端口SIN送来的异步数据,并进行串/并转换,此外,接收模块还包含模块控制和模块状态配置功能,用来设置接收数据帧的属性以及向中断仲裁模块输出状态信号;发送模块其作用是对从CPU送来的并行数据进行并/串转换,将串行数据从SOUT输出到串口,同接收模块相同,该模块也包含模块控制和模块状态配置功能;中断仲裁模块其作用是用来实现外部接口对内部寄存器的操作以及中断信号的仲裁操作,在UART的工作过程中,发送和接收模块的状态信号都送入该模块的线性状态寄存器中,经过内部的逻辑操作输出相应的中断信号,指示与UART相连的外部设备进行相应的读写操作;MODEM模块其作用是用来和外部的调制解调器或者其他的UART设备进行通信。2.1接收模块在接收的过程中,由于串行数据帧异步于接收时钟,因此,当检测到SIN由高电平到低电平的变化将被认为是一帧数据的开始位。为避免由于噪声引起的错误数据,本设计中实现了错误开始位检测功能,即要求开始位必须在收发波特率时钟的50%以上为低电平。由于我们采用的内部时钟其频率是波特率时钟的16倍,因此开始位至少在8个内部时钟周期内为低电平才被认为有效。一旦开始位被确认,后面的数据比特和校验比特将会每16个内部时钟周期采样一次。接收模块包括一个数据缓冲寄存器和一个接收移位寄存器。当检测到开始位有效时,其后的数据比特将会依次存人数据移位寄存器,根据数据帧的配置,当接收完所有数据比特后会根据奇偶校验是否被使能来判断下一步进行校验或停止接收,等待外部设备读取接收到的数据。整个过程可通过状态机方便的实现,状态转移图如图2所示。由图2不难看出,接收模块的状态机包含4个状态:空闲状态(idle)、移位状态(shift)、奇偶校验状态(parity)和停止位状态(stop)。其工作过程如下:当系统复位时,状态机进入idle状态,等待开始位,SIN由高电平变为低电平并被确认为有效的开始位后,状态机进入shift状态;shift状态中,接收模块为每一个数据比特移人等待16个内部时钟周期,接收完一帧数据后,若奇偶校验使能有效,跳转到parity状态,否则,进入stop状态;在parity状态中对奇偶校验比特进行采样,状态机将跳转到stop状态;状态机进入stop状态后,等待16个内部时钟周期后将对停止位的长度进行采样,而后进人idle状态。2.2发送模块在发送过程中,当发送数据装载到发送保持寄存器后,串行数据将自动使能从而进行数据传输。首先一个开始位被发送出去,同时发送数据由发送保持寄存器装载到发送移位寄存器中,而将数据以波特率时钟逐位发送出去,并按照线性控制寄存器的要求加上奇偶校验位和停止位。其时钟、帧结构配置和工作过程与接收模块类似,因此,发送模块也可以通过相似的状态机实现。2.3中断仲裁模块UART的中断分为4个等级,其对应的中断事件为:接收模块线性状态、接收数据准备就绪、发送保持寄存器空和MODEM状态,它们记录在中断识别寄存器中。UART通过读取中断识别寄存器检测所有的中断信号,然后指明优先级最高的中断给外部接口。该模块使用状态机实现时,共分为5个状态,其中4个等级的中断各为一个状态,外加一个空闲状态,根据每次读取中段识别寄存器的结果确定应进入哪一状态,从而保证了各级中断依次被响应。2.4MODEM控制器模块在UART中,MODEM控制器模块的作用是用来和外部的调制解调器或者其他的UART设备进行通信,它主要通过MODEM控制器和MODEM状态寄存器来进行具体操作。MODEM控制器用来控制DTRn(DataTerminalReady)和RTSn(RequestToSend)的输出状态。DCDn(DataCarrierDetect)、CTSn(ClearToSend)、DSRn(DataSetReady)和RIn(RingIndieator)的线性状态由MODEM控制模块来监控,同时存储于MODEM状态寄存器中。于UART的FPGA设计验证方法对于大多数FPGA设计来讲,UART也可以作为设计模块与PC的接口嵌入到FPGA芯片当中,通过RS232接口连接到计算机,使用相关的串口调试软件即可在计算机上对FPGA进行数据的输入,并且在显示器上直接观察到其输出的结果,这样就衍生出一种针对FPGA设计功能验证的直观有效的方法,即基于UART与串口调试软件的功能验证方法。该方法的关键在于如何将UART嵌入待验证的模块,本文以卷积编码加交织模块为例,详细介绍其与UART的连接方法,连接示意图如图3所示。在本方案中,每次实验由键盘输入26b数据,通过串口调试软件和UART发送到FPGA芯片,经码率为1/2的卷积编码后得到52b数据进行交织,交织后的数据分为4b一组送到UART发送模块,经UART通过串口发送到计算机上,最终在屏幕上看到编码和交织的结果。卷积编码模块采用Xilinx的IP核实现,该模块要求串行输入,而UART接收模块的输出为8位并行数据,故在他们之间加上并串转换模块。随着每一次并行数据的写入,并串转换模块会接收到一个写入的指示信号,同时开始顺序输出8位串行数据到卷积编码模块卷积编码器的输出是2位并行数据,由于先前的接收模块及串并转换模块每次处理8b数据的关系,故可以认为卷积编码器每次连续输出8个2位并行数据,而我们的系统要求每26个输入比特进行一次卷积编码和交织,所以在编码和交织之间连接一个FIFO作为数据缓冲,累计到26b数据后输出一次,同时设置其输入为2b并行,输出为串行,即实现了并串转换的功能,满足了交织器串行数据输入的要求。最后发送回计算机的数据为52b,所以对UART发送模块作了简单的修改,使其每次发送4b数据,这样就可以将52b分13次发完,同时为了实现交织器输出的连续数据与UART的衔接,我们在此处再加一个FIFO作为缓冲以及串并转换,将输入的串行数据变为4b并行数据逐次发送。这些模块的工作都由一些控制信号来指示,所以本例中采用了一个自己编写的控制信号模块来生成这些指示信号,比如每次UART接收到数据后即产生一个写入信号指示串并转换模块开始工作,同时在其输出有效时产生信号告诉编码器开始工作;同理,两个FIFO何时接收数据、何时输出数据以及交织器何时工作都受该模块产生的信号控制,这样,就能够保证多个模块协调统一的工作。将输入数据110101010101110101111111011001通过计算机发送到UART,按照每帧8b的要求将该26b的数据补0至32位,得到数据110101010101110101111111011001000000,转换成16进制为D55D7F40,写入FPGA进行编码交织再经由UART传回计算机得数据0D0E060B000C0C09030C040C0D,如图4所示。每8位数据取后4位得DE6B0CC93C4CD,转换为二进制得1101111001101011000011001100100100111100010011001101。通过Matlab进行理论验证,确为我们采用的(2,1,7)卷积编码(171,133)再经交织后得到的输出。同时该实验也验证了UART在实际应用中的效果。',)

提供UART,uart会员下载,编号:1700774163,格式为 docx,文件大小为3页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载