UART串口通信实验报告,uart串口通信原理

本作品内容为UART串口通信实验报告,格式为 docx ,大小 4047302 KB ,页数为 12页

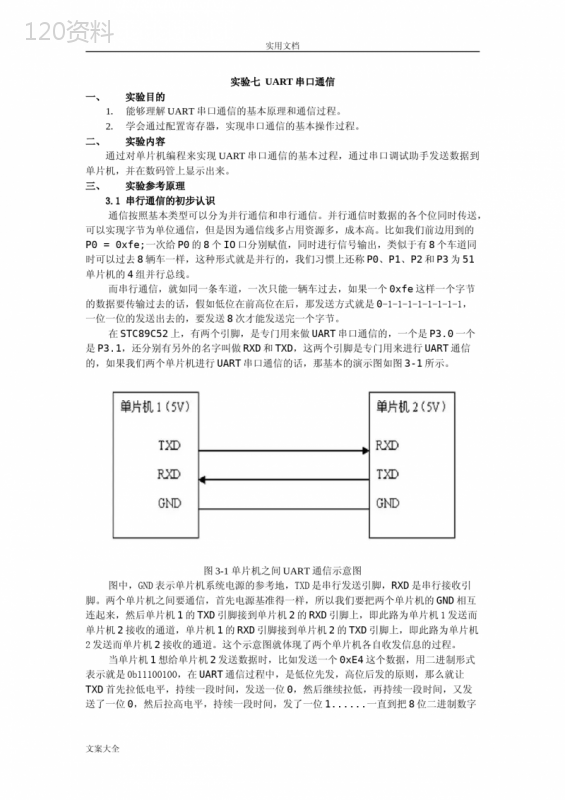

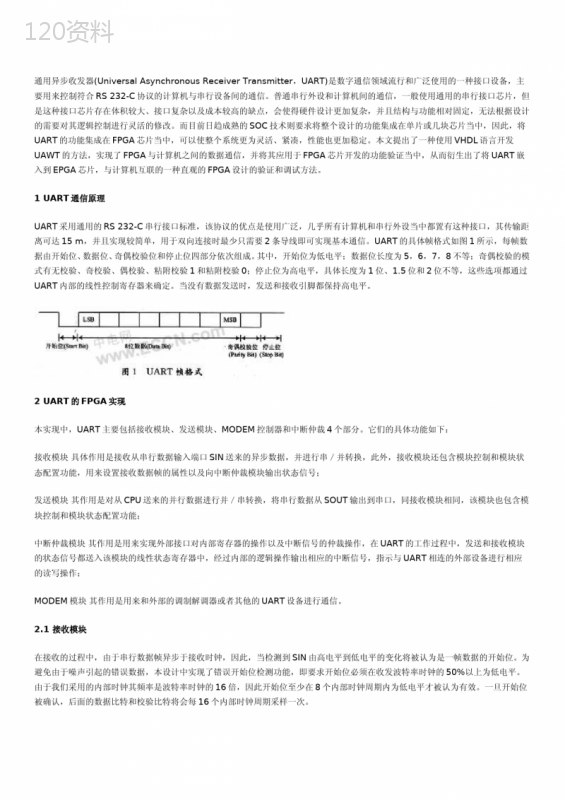

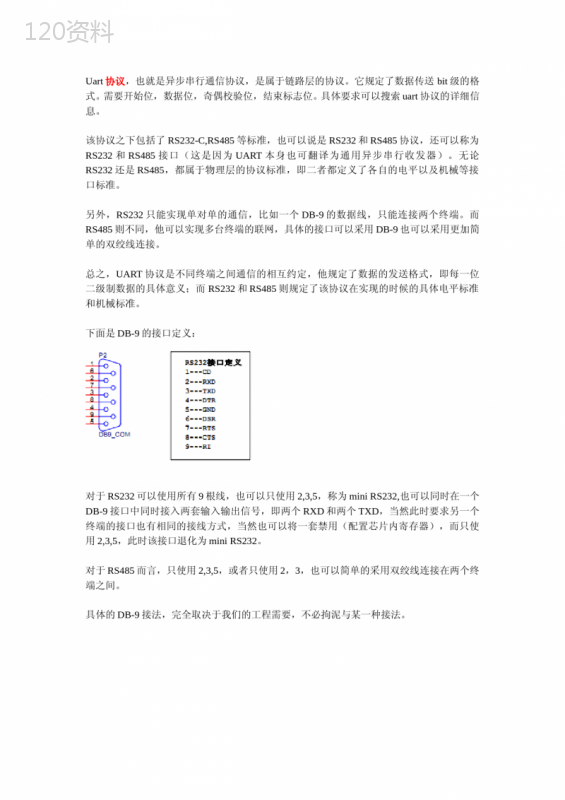

('UART串口通信实验报告现代电路与系统实验报告实验四UART串口通信学院:研究生院学号:1400030034姓名:张秋明一、实验目的及要求设计一个UART串口通信协议,实现“串<-->并”转换功能的电路,也就是“通用异步收发器”。二、实验原理UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM通信。UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。其中各位的意义如下:起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。资料位:紧接着起始位之后。资料位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从最低位开始传送,靠时钟定位。奇偶校验位:资料位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中两台设备间出现了小小的不同步。因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟同步的机会。适用于停止位的位数越多,不同时钟同步的容忍程度越大,但是数据传输率同时也越慢。空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。波特率:是衡量资料传送速率的指标。表示每秒钟传送的符号数(symbol)。一个符号代表的信息量(比特数)与符号的阶数有关。例如资料传送速率为120字符/秒,传输使用256阶符号,每个符号代表8bit,则波特率就是120baud,比特率是1208=960bit/s。这两者的概念很容易搞错。三、实现程序libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entityuartisport(clk:instd_logic;--系统时钟rst_n:instd_logic;--复位信号rs232_rx:instd_logic;--RS232接收数据信号;rs232_tx:outstd_logic--RS232发送数据信号;);现代电路与系统实验报告现代电路与系统实验报告现代电路与系统实验报告-----------------------------------------------------------------------------------------------------------------------3个子模块------------------------------------------------------------------------------异步接收模块-------------------------------------------libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityuart_rxisport(clk:instd_logic;--系统时钟rst_n:instd_logic;--复位信号rs232_rx:instd_logic;--RS232接收数据信号clk_bps:instd_logic;--此时clk_bps的高电平为接收数据的采样点bps_start:outstd_logic;--接收到数据后,波特率时钟启动置位rx_data:outstd_logic_vector(7downto0);--接收数据寄存器,保存直至下一个数据来到rx_int:outstd_logic--接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去);enduart_rx;architecturebehavofuart_rxissignalrs232_rx0:std_logic;signalrs232_rx1:std_logic;signalrs232_rx2:std_logic;signalrs232_rx3:std_logic;signalneg_rs232_rx:std_logic;signalbps_start_r:std_logic;signalnum:integer;signalrx_data_r:std_logic_vector(7downto0);--串口接收数据寄存器,保存直至下一个数据到来beginprocess(clk,rst_n)现代电路与系统实验报告beginif(rst_n=\'0\')thenrs232_rx0<=\'0\';rs232_rx1<=\'0\';rs232_rx2<=\'0\';rs232_rx3<=\'0\';elseif(rising_edge(clk))thenrs232_rx0<=rs232_rx;rs232_rx1<=rs232_rx0;rs232_rx2<=rs232_rx1;rs232_rx3<=rs232_rx2;endif;endif;neg_rs232_rx<=rs232_rx3andrs232_rx2andnot(rs232_rx1)andnot(rs232_rx0);endprocess;process(clk,rst_n)beginif(rst_n=\'0\')thenbps_start_r<=\'0\';rx_int<=\'0\';elseif(rising_edge(clk))thenif(neg_rs232_rx=\'1\')then--接收到串口数据线rs232_rx的下降沿标志信号bps_start_r<=\'1\';--启动串口准备数据接收rx_int<=\'1\';--接收数据中断信号使能elseif((num=15)and(clk_bps=\'1\'))then--接收完有用数据信息bps_start_r<=\'0\';--数据接收完毕,释放波特率启动信号rx_int<=\'0\';--接收数据中断信号关闭endif;endif;endif;endif;bps_start<=bps_start_r;endprocess;现代电路与系统实验报告process(clk,rst_n)beginif(rst_n=\'0\')thenrx_data_r<="00000000";rx_data<="00000000";num<=0;elseif(rising_edge(clk))thenif(clk_bps=\'1\')thennum<=num+1;casenumiswhen1=>rx_data_r(0)<=rs232_rx;--锁存第0bitwhen2=>rx_data_r(1)<=rs232_rx;--锁存第0bitwhen3=>rx_data_r(2)<=rs232_rx;--锁存第0bitwhen4=>rx_data_r(3)<=rs232_rx;--锁存第0bitwhen5=>rx_data_r(4)<=rs232_rx;--锁存第0bitwhen6=>rx_data_r(5)<=rs232_rx;--锁存第0bitwhen7=>rx_data_r(6)<=rs232_rx;--锁存第0bitwhen8=>rx_data_r(7)<=rs232_rx;--锁存第0bitwhen10=>rx_data<=rx_data_r;when11=>num<=15;whenothers=>null;endcase;if(num=15)thennum<=0;endif;endif;endif;endif;endprocess;endbehav;现代电路与系统实验报告---------------------------------波特率控制模块-----------------------------------------libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entityspeed_selectisport(clk:instd_logic;--系统时钟rst_n:instd_logic;--复位信号clk_bps:outstd_logic;--此时clk_bps的高电平为接收或者发送数据位的中间采样点bps_start:instd_logic--接收数据后,波特率时钟启动信号置位或者开始发送数据时,波特率时钟启动信号置位);endspeed_select;architecturebehavofspeed_selectissignalcnt:std_logic_vector(12downto0);signalclk_bps_r:std_logic;constantBPS_PARA:integer:=5207;constantBPS_PARA_2:integer:=2603;beginprocess(clk,rst_n)beginif(rst_n=\'0\')thencnt<="0000000000000";elseif(rising_edge(clk))thenif((cnt=BPS_PARA)or(bps_start=\'0\'))thencnt<="0000000000000";--波特率计数器清零elsecnt<=cnt+\'1\';--波特率时钟计数启动endif;endif;endif;endprocess;process(clk,rst_n)begin现代电路与系统实验报告if(rst_n=\'0\')thenclk_bps_r<=\'0\';elseif(rising_edge(clk))thenif(cnt=BPS_PARA_2)thenclk_bps_r<=\'1\';--clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点elseclk_bps_r<=\'0\';--波特率计数器清零endif;endif;endif;clk_bps<=clk_bps_r;endprocess;endbehav;---------------------------------异步发送模块-------------------------------------------libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityuart_txisport(clk:instd_logic;--系统时钟rst_n:instd_logic;--复位信号rs232_tx:outstd_logic;--RS232接收数据信号clk_bps:instd_logic;--此时clk_bps的高电平为接收数据的采样点bps_start:outstd_logic;--接收到数据后,波特率时钟启动置位rx_data:instd_logic_vector(7downto0);--接收数据寄存器,保存直至下一个数据来到rx_int:instd_logic--接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去);enduart_tx;architecturebehavofuart_txissignalrx_int0:std_logic;signalrx_int1:std_logic;现代电路与系统实验报告signalrx_int2:std_logic;signalneg_rx_int:std_logic;signalbps_start_r:std_logic;signalnum:integer;signaltx_data:std_logic_vector(7downto0);--串口接收数据寄存器,保存直至下一个数据到来beginprocess(clk,rst_n)beginif(rst_n=\'0\')thenrx_int0<=\'0\';rx_int1<=\'0\';rx_int2<=\'0\';elseif(rising_edge(clk))thenrx_int0<=rx_int;rx_int1<=rx_int0;rx_int2<=rx_int1;endif;endif;neg_rx_int<=not(rx_int1)and(rx_int2);endprocess;process(clk,rst_n)beginif(rst_n=\'0\')thenbps_start_r<=\'0\';tx_data<="00000000";elseif(rising_edge(clk))thenif(neg_rx_int=\'1\')then--接收到串口数据线rs232_rx的下降沿标志信号bps_start_r<=\'1\';--启动串口准备数据接收tx_data<=rx_data;--接收数据中断信号使能elseif((num=15)and(clk_bps=\'1\'))then--接收完有用数据信息bps_start_r<=\'0\';--数据接收完毕,释放波特率启动信号endif;endif;现代电路与系统实验报告endif;endif;bps_start<=bps_start_r;endprocess;process(clk,rst_n)beginif(rst_n=\'0\')thenrs232_tx<=\'1\';num<=0;elseif(rising_edge(clk))thenif(clk_bps=\'1\')thennum<=num+1;casenumiswhen1=>rs232_tx<=\'0\';when2=>rs232_tx<=tx_data(0);--发送第1bitwhen3=>rs232_tx<=tx_data(1);--发送第2bitwhen4=>rs232_tx<=tx_data(2);--发送第3bitwhen5=>rs232_tx<=tx_data(3);--发送第4bitwhen6=>rs232_tx<=tx_data(4);--发送第5bitwhen7=>rs232_tx<=tx_data(5);--发送第6bitwhen8=>rs232_tx<=tx_data(6);--发送第7bitwhen9=>rs232_tx<=tx_data(7);--发送第8bitwhen10=>rs232_tx<=\'1\';when11=>num<=15;whenothers=>null;endcase;if(num=15)thennum<=0;endif;endif;endif;endif;endprocess;endbehav;四、实验步骤现代电路与系统实验报告1、建立新工程UART,选择芯片,型号为cycloneiiEP2C35F484C8。2、建立源文件,输入程序代码。3、综合,编译。4、进行管教分配,分配截图如下5、把程序下载到板子,打开串口调试助手,进行实验。五、实验结果程序下载成功后,在串口调试助手界面中,串口设置为COM1,波特率设为9600,数据位设为8,然后在发送栏输入2个16进制的数据,点发送后,会在数据接收栏收到这两个数据。',)

提供UART串口通信实验报告,uart串口通信原理会员下载,编号:1700774164,格式为 docx,文件大小为12页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载