基于DDS的高精度信号发生器的设计

本作品内容为基于DDS的高精度信号发生器的设计,格式为 doc ,大小 1438720 KB ,页数为 43页

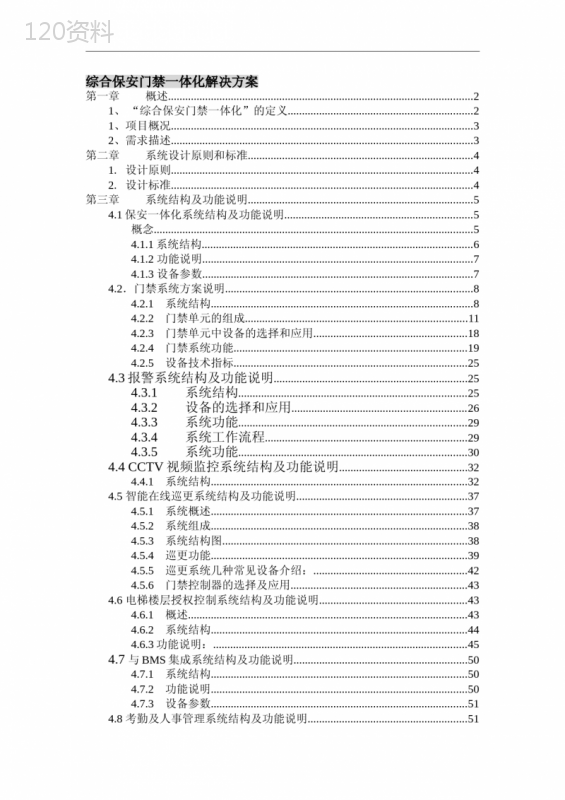

('基于DDS的高精度信号发生器的设计摘要频率源是雷达、通信、电子对抗与电子系统实现高性能指标的关键,很多现代电子设备和系统的功能都直接依赖于所用频率源的性能,因此频率源被人们喻为众多电子系统的“心脏”。直接数字频率合成(DDS)是近年来发展起来的一种新的频率合成技术。其主要优点是相对带宽很宽、频率转换时间极短(可小于20ns)、频率分辨率很高、全数字化结构便于集成、输出相位连续、频率、相位和幅度均可实现程控。因此,能够与计算机紧密结合在一起,充分发挥软件的作用。作为应用,现在己有DDS产品用于接收机本振、信号发生器、通信系统、雷达系统、跳频通信系统等。本系统采用AT89C52单片机和AD9851为核心,辅以必要的模拟,数字电路,构成了一个基于DDS技术的信号发生器。该软件系统采用44键盘操作,以菜单形式进行显示,操作方便简单,软件增加了许多功能。它通过启动DDS把内存缓存区的数据读出送到DDS后输出相应的频率,并把数据转换为BCD码,通过数码管进行显示。该系统体积小、稳定度、精度极高,方便携带,适用于当代的尖端的通信系统和精密的高精度仪器以及高频无线传输系统等。关键词:信号发生器,DDS,AT89C52,AD9851IDDS-basedHighPrecisionSignalGereratorABSTRACTThefrequencysourceistheradar,thecorrespondence,theelectroniccountermeasureandtheelectronicsystemrealizationhighperformancetargetkey,theverymanymodernelectronicinstallationandthesystemfunctionalldirectlyreliesoninusesthefrequencysourcetheperformance,thereforethefrequencysourceisexplainedbythepeopleforthemultitudinouselectronicsystem;theheart;.Thedirectdigitalfrequencysynthesizes(DDS)isonekindofnewfrequencysynthesistechnologywhichtherecentyearsdeveloped.ltsmainmeritistherelativebandwidthisverywide,thefrequencyswitchingtimeisextremelyshort(maysmallthan100ns),thefrequencyresolutionisveryhigh,theentiredigitizedstructureisadvantageousfortheintegration,theoutputphasecontinuously,thefrequency,thephaseandthescopemayrealizetheprogramcontrol.Therefore,canunifycloselyinwiththecomputertogether,fullydisplaysthesoftwarethefunction.Astheapplication,hadtheDDSproducttouseinthereceiverlocaloscillation,thesignalgeneratingdevice,thecommunicationssystem,theradarsystem,thefrequency-hoppingcommunicationssystemnowandsoon.ThissystemusestheAT89C52andAD9851areacore,auxiliarybynecessitysimulation,digitalcircuit,constitutedonebasedontheDDStechnologysinewavesignalgeneratingdevice.Thissoftwaresystemusesthe44keyboardoperation,carriesonthedemonstrationbythemenuform,theeaseofoperationissimple,thesoftwareincreasedmanyfunctions.ItthroughstartsDDS,afterdeliversthememorybufferareadataread-outDDStooutputthecorrespondingfrequency,andthedataconversionistheBCDcode,carriesonthedemonstrationthroughtheLEDdisplay.Thissystemvolumesmall,thestability,theprecisionareextremelyhigh,facilitatethecarryhome,issuitableincontemporaryII[onlinetranslation]andsoonacmecommunicationssystemandpreciseprecisioninstrumentaswellashighfrequencywirelesstransmissionsystem.KEYWORDS:SignalGererator,DDS,AT89C52,AD9851目录摘要..............................................................................................................................IABSTRACT..............................................................................................................................II目录..........................................................................................................................III1绪论..............................................................................................................................11.1频率合成技术概述.........................................................................11.2直接数字频率合成技术的应用与现状.................21.3信号发生器概况................................................................................31.3.1信号发生器分类......................................................................41.3.2各类信号发生器特点........................................................41.4系统设计方案.......................................................................................61.5本文研究的主要内容..................................................................71.6本章小节.....................................................................................................72直接数字频率合成....................................................................................82.1存储器与波形数据.........................................................................82.2波形发生器的系统组成...........................................................82.3采用DDS方式的波形发生器.................................................82.3.1相位累加器....................................................................................92.3.2查询表ROM...........................................................................................102.3.3数模转换器................................................................................102.4DDS输出频谱...........................................................................................102.5DDS设计中的参数选择...............................................................112.6本章小节..................................................................................................113硬件设计............................................................................................................123.1总体介绍..................................................................................................123.2微控制器..................................................................................................13III3.3DDS模块.........................................................................................................143.4显示模块..................................................................................................163.5低通滤波器的设计......................................................................163.6本章小结..................................................................................................184软件实现............................................................................................................194.1主监控程序模块.............................................................................194.2键盘扫描模块....................................................................................204.2.1键盘简述.......................................................................................204.2.244矩阵键盘的编程方法.............................................214.3频率控制字的送入模块........................................................224.4数码管显示程序的编程方法..........................................234.5本章小结..................................................................................................255结束语...................................................................................................................26致谢..........................................................................................................................27参考文献................................................................................................................28附录..........................................................................................................................30IV基于DDS的高精度信号发生器的设计1绪论1.1频率合成技术概述频率合成是指一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性计算,产生具有同样稳定度和精确度的大量离散频率的过程。实现频率合成的电路叫频率合成器,频率合成器是现在电子技术的重要组成部分。在通信,雷达、导航等技术中,频率合成器既是发射机的激励信号源,又是接收机的本地振荡器。在电子对抗设备中,它可以作为干扰信号发生器,在测试设备中,可作为标准信号源,因此频率合成器被人成为许多电子系统的心脏。随着电子技术的不断展,对频率合成器的要求越来越高,频率合成器的主要性能指标有;(a)输出频率范围频率范围是指频率合成器输出最低频率和输出最高频率之间的变化范围,它包含中心频率和带宽两个方面的含义[1]。(b)频率稳定度频率稳定度是指规定的时间间隔内,频率合成器输出频率偏离标准值的数值,他分长期、短期和瞬间稳定度三种。(c)频率间隔频率间隔是指两个输出频率之间的最小间隔,也称频率分辨率。(d)频率转换时间频率转换时间是指输出频率由一个频率转换到另一个频率的时间。(e)频率纯度频率纯度以杂散分量和相位噪声来衡量。杂散又称寄生信号,分为谐波分量和非谐波分量两种。1陕西科技大学毕业设计说明书主要由频率合成过程中的非线性失真产生,相位噪声是衡量输出信号相位抖动的大小的参数[2]。(f)调制性能调制性能是指频率合成器的输出具有调幅(AM),调频(FM),调相(PM)等功能。频率合成器的实现方法有三种:直接模拟频率合成、间接频率合成、直接数字频率合成。直接模拟频率合成技术是一种早期的频率合成技术,它用一个或几个参考频率源经谐波发生器变成一系列谐波,再经混频、分频、倍频和滤波等处理产生大量的离散频率[3]。这种方法的优点是频率转换时间短、相位噪声低,但由于采用大量的混频、分频、倍频和滤波等途径,使频率合成器的体积大,成本高,结构复杂,容易产生杂散分量,且难于抑制。间接频率合成技术又称锁相式频率合成,它是利用锁相技术实现频率的加、减、乘、除。其优点是由于锁相环路相当于一窄带跟踪滤波器,因此能很好地选择所需频率的信号,抑制杂散分量,且.避免了大量使用滤波器,十分有利于集成化和小型化。此外,一个设计良好的压控振荡器具有高的短期频率稳定性,而标准频率源具有高的长期频率稳定度,锁相式频率合成器把这两者结合在一起,使其合成信号的长期频率稳定度和短期频率稳定度都很高。但锁相式频率合成器的频率转换时间较长,单环频率合成器的频率间隔不可能做得很小[4]。直接数字频率合成(DDS—DigitalDirectFrequencySynthesis)技术是一种全新的频率合成方法,是频率合成技术的一次革命。这种技术首先由美国学者J.Tierny,C.M.Rader和B.Gold三人于1971首次提出,但限于当时的技术和工艺水平,DDS技术仅仅在理论上进行了一些探讨,而没有应用到实际中去。DDS是一种全数字化的频率合成器、由相位累加器、波形ROM、D/A转换器和低通滤波器构成。2基于DDS的高精度信号发生器的设计时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。DDS有如下优点:(1)频率分辨率高,输出频点多;(2)频率切换速度快;(3)频率切换时相位连续;可以输出宽带正交信号;(4)输出相位噪声低,对参考频率源的相位噪声有改善作用;(5)可以产生任意波形;(6)全数字化实现,便于集成,体积小,重量轻。随着微电子技术的飞速发展,目前市场上性能优良的DDS产品不断推出,如美国QUALCMOMM公司的Q2334,Q2220等DDS芯片;美国STANFORD公司的STEL-1175,STEL-1180等DDS芯片;美国AD公司的AD7008,AD9850等DDS芯片。这些DDS芯片的时钟频率从几十兆赫兹到几百兆赫兹不等[5]。1.2直接数字频率合成技术的应用与现状由于DDS的特点以及一些公司不断推出的DDS芯片和产品,DDS技术被广泛应用于雷达、通信、电子对抗和仪器仪表等领域。事物都带有两面性。DDS的全数字结构也给它带来了两个缺点,一个是输出杂散较大,另一个是输出带宽受到限制。DDS有三个杂散源:相位截断、幅度量化和D/A转换器的非理想特性[6]。DDS输出带宽受限是由于数字器件的工作频率不能很高以及DDS本质上是一个分频器引起的。为了克服DDS输出杂散大的缺点,国内外学者对DDS输出频谱特性进行了大量研究,HenryT.Nicholc-A:和ElenrvSamueli等人用误差信号分析法来分析相位截断误差,他们建立了相位截断误差的数学模型,利用数论对相位截断误差的谱线位置和功率进行了较为精确的研究。根据他们的研究结果,只要知道了相位累加器字长、波形ROM地址线位数和频率控制字,就可预测出相位截断误差的潜线位置和幅度。国内学者采用严格的数学方法,分析了3陕西科技大学毕业设计说明书理想DDS的频谱结构,推导出了相位误差信号的谱函数并分析了其分布规律,得到了相位截断条件下DDS杂散分布的规律性。还有一种波形分析法,它根据DDS中相位累加器的周期性以及实际DDS的结构,得到DDS输出波形的数学描述,然后对得到的波形进行Fourier级数分析[7]。波形分析法简单、直接、计算量大,但借助于计算机和FFT技术,这一分析方法还是相当有效的。在分析DDS输出频谱特性的基础上提出了一些降低杂散功率的方法,归纳起来有三种:优化设计波形ROM和相位累加器、用随机抖动法提高无杂散动态范围、以过采样的方法降低带内误差功率[8]。为了提高DDS输出频率,一方面一些半导体公司利用目前最先进的半导体集成技术不断提高DDS芯片本身的工作频率[9],另一方面很多学者和单位把DDS技术和其它方法组合起来以扩展输出频率。例如当输出信号频率高而带宽较窄时,可以利用移相技术或混频滤波法扩展DDS输出频率。在组合式频率合成技术中,DDS+PLL组合式频率合成器是一种扩展DDS频率的有效方法,它兼顾DDS和PLL两者的优点。DDS+PLL组合方式分DDS激励PLL的锁相倍频方式和PLL内插DDS的方式。DDS是一项充满生命力的技术,其发展速度和应用范围之广是惊人的,从七十年代到今天,西方国家从未间断过对DDS技术及其应用的研究,一批批成功的DDS芯片和DDS应用产品正在逐步获得国际市场的青睐[10]。我国对DDS的研究刚刚起步,存在大量的艰巨工作要做,如精确分析DDS的杂散频谱特性,研究DDS杂散功率降低方法以及扩展DDS的输出带宽,以发挥其频率分辨率高、频率切换快、相位噪声低和全数字化等优点,使DDS技术在国内得到广泛应用。4基于DDS的高精度信号发生器的设计1.3信号发生器概况信号发生器是一种历史最为悠久的测量仪器。早在二十年代,当电子设备刚开始出现时,它就出现了。随着通信和雷达技术的发展,四十年代出现了主要用于测试各种接收机的标准信号发生器,使信号发生器从定性分析的测试仪器成为定量分析的测量仪器,同时,还出现了可用来测试脉冲电路或用作脉冲调制器的脉冲信号发生器。由于早期的信号发生器机械结构比较复杂,功率比较大,电路比较简单(与数字仪器、示波器等相比),因此,发展速度较慢。直到1964年才出现了第一台全晶体管的信号发生器。自六十年代以来,信号发生器有了迅速的发展,出现了函数发生器、扫频信号发生器、合成信号发生器、程控信号发生器等各种新的种类,而且,各类信号发生器的主要性能指标也都有了大幅度的提高。与此同时,各类信号发生器在简化机械结构,体积小型化、功能多样化等各方面也取得了显著的进展。信号发生器是一种常用的信号源,被广泛应用于电子电路、自动控制和科学试验等各个领域。它是一种为电子测量和计量工作提供符合严格技术要求的电信号设备。如:在测试、研究或调试电子电路及设备时,为测定电路的一些电参量,如测量频率响应、噪声系数、为电压表定度等,都要求提供符合所定技术条件的电信号,以模拟在实际工作中使用的待测设备的激励信号。另外,当要求进行系统的稳态特性测量时,需使用振幅、频率已知的正弦信号源。1.3.1信号发生器分类信号发生器是许多电子设备特别是测试设备必备的一部分,用以输入基准源信号给被测设备,通过接收被测设备返回的信息,来分析研究被检测设备的情况。广义的信号发生器有许多种类,5陕西科技大学毕业设计说明书如光纤传感器中光纤陀螺仪的发光二极管等。狭义上讲,信号发生器是指电子设备中的纯粹电信号发生器。对本论文来讲,我们将范围缩小到正弦电信号发生器上[11]。我们衡量或评定一个信号发生器的精度时,主要是对其中最基本和最重要的部分即正弦信号进行检测。检验正弦信号性能的重要指标是频率准确度和频率稳定度、信噪比和谐波畸变[12]。信号发生器大致可分为两类:模拟振荡式和数字式,具体如图1.1所示。图1.1信号信号发生器分类1.3.2各类信号发生器特点各类信号发生器输出信号精度不一样,适合于不同的需求情况。按照不同的精度要求来选用信号发生器,既可以满足技术指标上的要求,又可以最大限度地控制成本。下面将对图1.1所列的各种信号发生器逐类进行工作原理分析和优缺点比较。(a)首先介绍模拟振荡式信号发生器[13],振荡器是一种可自动地将直流电源的能量转换为一定波形的交变振荡能量的装置。振荡器的种类有很多,从振荡电路中有源器件的特性和形成振荡的原理来看,可把振荡器分为反馈式振荡器和负阻式振荡器两类。前者是利用有源器件和选频电路根据正反馈原理所组成的振荡电路,后者是把一个呈负阻特性的二端有源器件直接与振荡点录像连接。6基于DDS的高精度信号发生器的设计按照输出信号又可以分为正弦波振荡器和非正弦波振荡器(张驰振荡器)。一个简单的电容反馈三端式模拟振荡式信号发生器基本原理如图1.2,振荡器输出的正弦波工作频率近似等于并联回路的谐振频率。模拟振荡式信号发生器是最简单的一种信号发生器。优点是器件数量少,线路简单,制造成本低,易于调试。缺点是难以获得很高的输出信号精度和稳定度。一般只用于一些对精度要求不太高的设备中[14]。图1.2模拟振荡式信号发生器(b)数模转换型信号发生器基本原理是:首先将连续正弦信号抽样并量化使之成为数字正弦信号存入ROM或EPROM中,然后通过查表周期地读出这些数字样值并送往D/A转换器[15],最后经模拟低通滤波器平滑后,输出所需要的模拟正弦信号,其基本工作框图如下图1.3所示:图1.3模数转换型基本结构现在在理论上对数模转换型信号发生器进行精度分析,采用这种数字方式时,设每周期正弦信号的等间隔抽样点数为N,读ROM表的时钟频为FR,则所产生的正弦信号频率f=FR/N[16],因为N是确定的值,所以所产生正弦信号的频率准确度与稳7陕西科技大学毕业设计说明书定度完全由读码频率决定,而读码频率可由晶体振荡器通过数字分频得到,晶体振荡器的输出精度能达到几十个PPM,因此数模转换型信号发生器有较高的频率准确度和稳定度。但是检验正弦信号的重要指标除了频率准确度和频率稳定度外,还有信噪比和谐波畸变两项。数模转换型信号发生器的噪比和谐波畸变主要取决于数模转换器的位数和精度,由于高位的数模转换器制造困难,造价较高,使得该类高精度的信号发生器制造成本很高,而且也限制了信号发生器精度的进一步提高。本文所设计的信号发生器就属于此类型。(c)Σ-△数字调制信号发生器有ROM型和DSP型之分[17],是一种高精度信号发生器,用到了Σ-△数字调制技术。该类发生器能较好地解决正弦信号所有四个指标精度问题,而且也比较稳定。当然,相对于数模转换型信号发生器,该类型发生器制造成本非常高。另外,采用DSP方式生成数字正弦信号时,是利用DSP硬件技术来实时模拟Σ-△调制器的响应,因此可以实时产生不同频率的正弦信号。Σ-△调制又称为总和增量调制,是数字通讯系统中的一种波形编码技术。Σ-△调制技术是当今地质勘探界所有24位大型遥测地震仪器系统的核心技术,它是伴随着高位ADC的发展而发展起来的。Σ-△调制器同以往的均匀量化(PCM),A/D转换器的量化过程有所不同,它不是直接根据抽样数值的每个样值的大小进行量化编码,而是根据前一样值与后一样值之差即所谓增量的大小进行量化编码。Σ-△调制器以极高的抽样频率对输入的模拟信号进行抽样,并对两个抽样之间的插值进行低位量化,从而得到用低位数码表示的数字信号,即Σ-△代码[18]。1.4系统设计方案方案一:用分立元件组成的函数发生器。通常是单函数发生器且频率不高,其工作不很稳定,8基于DDS的高精度信号发生器的设计不易调试。方案二:可以由晶体管、运放IC等通用器件制作,更多的则是用专门的函数信号发生器IC产生。早期的函数信号发生器IC,如:L8038,BA205,XR2207/2209等,功能较少,精度不高,频率上限只有300kHz,无法产生更高频率的信号,调节方式也不够灵活,频率和占空比不能独立调节[19],二者互相影响。方案三:采用传统的直接频率合成器对模拟信号进行频率合成。使用这种方法,可以使频率合成速度快、噪声低,但需要以引入大量分频、倍频、混频和滤波电路为代价,这就使得电路复杂、体积庞大、成本高,电路调试困难[20]。而且,这种设计方法只能实现标准波形的频率合成,对于我们所要求的对标准波形的线性叠加却无法实现。方案四:采用锁相环式频率合成器对模拟信号进行频率合成。采用这种方法,避免了使用大量的分频、倍频和滤波电路,使电路大大减化。但是,由于锁相环本身是一个惰性环节,频率转换时间较长,无法实现高精度的高频合成。而且,通过模拟手段产生的信号幅度、频率等参数很不稳定,并且电路同样无法实现对标准波形的线性叠加。方案五:自行设计的基于FPGA芯片的解决方案[21]。采用直接数字频率合成技术(DirectDigitalFrequencySynthesis简称DDS或DDFS,将所需的波形量化数据先存于存储器中,通过锁相环构成的频率合成器产生所需频率的脉冲驱动地址计数器,这样在存储器的数据线上会以所需频率出现波形数据,该数据经数模转换及滤波整形后,即得到相应的波形DDS技术的实现依赖于高速、高性能的数字器件。可编程逻辑器件以其速度高、规模大、可编程,以及有强大EDA软件支持等特性,十分适合实现DDS技术。但是就FPGA的制造工艺而言,FPGA在掉电后数据会丢失,上电后必须进行一次配置,因此FPGA在应用中需要为电路配置一定的程序。并且,FPGA9陕西科技大学毕业设计说明书器件作为一个数字逻辑器件,竞争和冒险正是数字逻辑器件较为突出的问题,因此,在使用时必须注意毛刺的产生、清除及抗干扰,这就增大了电路和程序的复杂程度和可实施性。方案六:利用专用的直接数字合成DDS芯片函数发生器。能产生任意波形并达到很高的频率[22],并且能很好的进行编程,使用方便有效。为了达到高精度,高稳定的正弦信号输出我们选择了第六种方案。1.5本文研究的主要内容了解一些信号发声器和频率合成的的基本知识并了解DDS的相关原理并利用单片机和DDS芯片来制作高精度的信号发生器。在这过程中加深对矩阵键盘原理的理解及运用,并了解滤波器的相关知识。1.6本章小节本章首先对频率合成技术的发展做了简单回顾接着重点介绍了DDS的应用和现状。接下来对信号发生器也做了一些概述,并对信号发生器进行了分类介绍。最后对本文的主要研究内容进行了阐述。10基于DDS的高精度信号发生器的设计2直接数字频率合成2.1存储器与波形数据如果一个存储器(这里以ROM为例)有n条地址线,则这个存储器的存储空间为2n。假如在2n个存储单元内存放了一个周期的正弦波形数据,则每个单元内的数据就表示正弦值的大小,这种存储器称为波形数据存储器。如果重复地从0~2n-1单元读出波形数据存储器中的数据,在波形数据存储器的输出端就会得到周期的正弦序列:如果将周期的正弦序列输入到D/A转换器,则会在D/A转换器的输出端得到连续的正弦电压或电流。输出正弦序列的周期是由读出数据的时钟频率决定的。设CLK为加于波形数据存储器的时钟,该时钟的周期为T0,则其频率为fclk=1/T0。显然,时钟频率越高,读取波形数据存储器内一个周期的数据所用的时间就越短,因而D/A转换器得到的正弦信号的频率就越高。2.2波形发生器的系统组成如图2.1所示为波形发生器的系统组成,时钟fclk加于二进制计数器,生成波形数据存储器所需的地址信号,地址信号的产生频率正比于时钟频率。计数器的输出在0~2n一1之间周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形11陕西科技大学毕业设计说明书[23]。图2.1波形发生器的系统组成2.3采用DDS方式的波形发生器在实际问题中,如果连续改变时钟频率fclk的值,就可以得到一个频率连续变化的周期信号。用LRC组成的虽然可以得到一个连续变化的时钟,但其频率稳定性很不好,且不可能得到一个宽范围变化的时钟信号。如果用晶体振荡器作为时钟,可以得到稳定度极高的时钟,但又不能满足频率可变的要求。如图2.2所示的电路既解决了频率稳定度的问题,又能灵活地改变频率变化范围,这就是DDS方式的波形发生器。可以看出,地址加法器和数据锁存器组成DDS电路。加法器有两个数据输入端,一个为DATA(在此称为频率数据),另一个为与数据存储器相连的B。为说明方便,假设地址加法器数据宽度为11,波形数据存储器有8条地址线[24]。图2.2采用DDS方式的波形滤波器DDS电路工作原理如下:在频率数据DATA的控制下,地址加法器的输出结果为DATA+B,因此,在时钟fclk的作用下,数据锁存器的数据将每次增加12基于DDS的高精度信号发生器的设计DATA。也就是说,DATA控制了地址加法器输出的递增速率。此例中,DATA最小为1,最大为23一1=7。在时钟频率fclk不变的情况下,DATA的大小控制了D10-DO从最小到最大变化所用的时间。DATA大,每次运算的结果较前一次的数据增长就大,因而地址数据循环一周(从D10-DO最小到D10-DO最大)所需时间就短,这意味着D/A转换器输出的波形频率就高。反之则相反。如果将数据D10-DO分为两部分:取高8位D10-D3与波形数据存储器相连(假设波形数据存储器的地址线共有8条),将D2-DO空下不用,这样,即使在DATA为最大(DATA=7)的情况下,D10-D3的数据增长也不会大于1,从而能够做到在逐一地从波形数据存储器读取数据,保证输出数据的精度。DATA的变化控制了D10-D3的数据变化速率,相当于DATA一定,而时钟fclk改变。DDS的基本结构包括相位累加器、正弦查y表ROM、数模转换器(DAC)以及低通滤波器等,如图2-1所示其中相位累加器和正弦查询表ROM合称为数控振荡器CNCO。下面将予以介绍。2.3.1相位累加器相位累加器是DDS最基本的组成部分,用于实现相位的累加并存储其累加结果。若当前相位累加器的值为Σn,经过一个时钟周期后变为Σn+1,则满足:Σn+1=Σn+FCW(2-1)由式(2-2)可见,Σn为一等差数列,不难得出:Σn=nFCW+Σ0(2-2)其中Σ0为相位类加器的初始相位值。相位累加器的基本结构如图2-3所示,它由一个Abits加法器和一个Abits寄存器构成,寄存器通常采用A个D触发器来构成。在此基础上,有人提出了改进的相位累加器结构,如图2-4所示,该结构降低了输出频谱对相位累加器初始状态值的依赖程度,可降低杂散幅度约4dB。13陕西科技大学毕业设计说明书图2.3相位累加器基本结构图2.4改进的相位累加器结构2.3.2查询表ROMDDS查询表ROM所存储的数据是每一个相位所对应的一进制数字正弦幅值,在每一个时钟周期内,相位累加器输出序列的高P位对其进行寻址,最后输出为该相位对应的一进制正弦幅值序列。可以看出ROM的存储量为2PXS比特。其中P为相位累加器的输出位数,S为ROM的输出位数。若P=12,S=8,可以算出ROM的容量为32768比特。在一块DDS芯片上集成这么大的ROM会使成本提高,功耗增大,日可靠性下降,所以就有了许多的压缩ROM容量的方法。而且容量压缩了还可以使用更大的P和S值,进而使DDS的杂散性能提高。2.3.3数模转换器DAC数模转换器的作用是将数字信号转变成模拟信号。而实际上由于DAC分辨率有限,其输出信号并不能真正地连续可变,所以只能输出阶梯模拟信号。DAC有电压和电流输出两种,美国ADI公司的DDS芯片内部都集成有DAC,称为complete-DDS,这种结构简化了DDS的系统设计。如果没有集成DAC,例如Qualcomm公司的某些芯片,此时为系统正确地选择DAC是一个十分关键的问题,因为DAC的性能直接决定整个系统的性能。14基于DDS的高精度信号发生器的设计2.4DDS输出频谱理想的DDS满足:(a)相位累加器的输出我;全部用来作寻址ROM的地址码,即A=P(如图2-1);(b)ROM存储的幅度值没有量化误差,即DAC的分辨率为无穷大;(c)DAC不存在转换误差,完全理想。在上述条件下,整个DDS相当于一理想的采样一保持电路。理想DDS的输出频谱。除所需要的频率外,在频率为nf0士f0的地方还有不需要的频谱分量,如图2-5所示。图2-5想采样的DDS输出频谱图我们可以发现理想DDS的输出即为所需的基频信号,并且在所有谱线中幅度最大,另外我们还注意到在nf0处没有谱线。在典型的DDS应用中,DDS后通常接有一个低通滤波器LPF,用它来滤除一阶镜像。而实际中LPF都有一个过渡带的问题,所以为了更好地消除一阶镜像带来的杂散,一般将DDS的输出频率限制在0~40%f0内。由于孔径失真带来的SIN(X)/X包络,使得DDS的输出幅度在Nyquist带宽内有大约3.92dB的下降。因此有的公司推出DDS芯片(如ADI的AD9858)中含有一个特性为X/SIN(X)的预失真波滤波器,它可以把DDS的输出幅度波动限制在0.1dB内。DDS输出的频谱实际上没有图2-5那样纯净,而是有许多多余的谱线,了解这个在DDS的设计中是十分必要的。2.5DDS设计中的参数选择波形数据存储器的全部数据被读出一次的频率为:15陕西科技大学毕业设计说明书f=(fclkxDATA)/2m(2-3)式中:f:波形数据存储器输出信号的频率;fclk:系统的时钟频率;m:地址加法器的数据宽度;DATA:频率控制字。2.6本章小节本章介绍了存储器和波形发生器的工作原理,在此基础引出了DDS信号发生器,介绍了DDS信号发生器的工作原理,并分块介绍了其内部结构,最后描述了它的频谱和参数选择,对直接数字频率合成技术(DDS)有了深入的了解。3硬件设计3.1总体介绍该系统是一种输出信号的频率随时间在一定范围内反复变化的正弦信号发生器。它是一种信号激励装置,用它所产生的正弦波来检测被测系统的频率响应,包括幅频响应和相频响应。当然,只要在波表存储器中存储其他类型的波表数据,就可以产生相应类型的信号,如方波、三角波、锯齿波等。本系统由CPU(AT89C52),DDS芯片、滤波器、键盘、LED显示器等单元组成,原理图如图3.1,其PCB图如附图Ⅲ-1。16基于DDS的高精度信号发生器的设计17陕西科技大学毕业设计说明书图3.1整体原理图3.2微控制器系统选用Atmel公司的AT89C52芯片来进行设计。其芯片引脚图如图3.2[25]。18基于DDS的高精度信号发生器的设计图3.2AT89C52的引脚图AT89C52单片机属于AT89C51单片机的增强型[26],与Intel公司的80C52在引脚排列、硬件组成、扩工作特性和指令系统等方面完全兼容[27]。其主要工作特性是:·片内程序存储器内含8KB的Flash程序存储器,可擦写寿命为1000次;·片内数据存储器内含256字节的RAM;·具有3个可编程定时/计数器;·中断系统具有8个中断源、6个中断矢量、2级优先权的中断结构;·串行口是具有一个可编程串行通信口;·具有一个数据指针DPTR;·低功耗工作模式有空闲模式和掉电模式;·具有可编程的3级程序锁定位;·工作电源电压为5(士0.2)V,且典型值为5V,是低电压单片机;·最高工作频率为24MHz。与AT89C51相比,增加了如下功能:·程序存储器由4KB增加到8KB;·片内RAM由128字节增加到256字节;·定时/计数器由2个增加到3个;·P.0和P1.1口增加了第二功能;·中断系统由6个中断源增加到8个,中断矢量由7个增加到6个。选用DIP封装形式。该系统CPU硬件资源分配如下:·信号幅度P0.0~P0.7;·键盘输入P1.0~P1.5;·扫速信号P2.0~P2.3;·点频/扫频控制信号P2.7(0为点频状态,1为扫频状态);·显示输出P3.0,P3.1,Pl.7(P3.0为控制线,P3.1为时钟线,Pl.7为数据线);·档位控制字P3.2-P3.4;·定时/计数器0工作在定时方式;19陕西科技大学毕业设计说明书·定时/计数器1工作在计数方式;·程序区EA接高电平,对ROM的读操作从内部程序存储器开始;·数据区选用内部数据区。3.3DDS模块DDS模块AD9851引脚图及接线如图3.3。AD9851是ADI公司采用先进的DDS技术推出的高集成度DDS频率合成器,它内部包括可编程DDS系统、高性能DAC及高速比较器,能实现全数字编程控制的频率合成和时钟发生。AD9851接口功能控制简单,可以用8位并行口或串行口直接输入频率、相位等控制数据。32位频率控制字,在180MHz时钟下,输出频率分辨率达0.0372Hz。先进的CMOS工艺使AD9851不仅性能指标一流,而且功耗低,在3.3V供电时,功耗仅为155Mw。图3.3AD9851引脚及接线图各引脚介绍:·D0~D7:8位数据输入口,可给内部寄存器装入40位控制数据;·PGND:6倍参考时钟倍频器的地;·PVCC:6倍参考时钟倍频器电源;·W—CLK:字装入信号,上升沿有效;·FQ—UD:频率更新控制信号,时钟上升沿确认输入数据有效;·REFCLOCK:外部参考时钟输入;20基于DDS的高精度信号发生器的设计·AGND:模拟地;·AVDD:模拟电源(+5V);·DGND:数字地;·DVDD:数字电源(+5V);·RSET:外部复位连接端;·VOUTN:内部比较器负向输出端;·VOUTP:内部比较器正向输出端;·VINN:内部比较器负向输入端;·VINP:内部比较器正向输入端;·DACBP:DAC旁路连接端;·IOUTB:互补DAC输出;·IOUT:内部DAC输出端;·RESET:复位端。3.4显示模块显示模块硬件原理图如图3.4所示。本系统采用8段数码显示管。四位整数部分和一位小数部分,数码管的输入与AT89C52的P2口相连,采用P3.3~P3.7与数码管的公共段相连来进行选择,由于AT89C52的驱动不够,所以在P3口后接放大器,再对数码管进行驱动.21陕西科技大学毕业设计说明书图3.4显示模块原理图3.5低通滤波器的设计需在其信号输出端接一个低通滤波器。滤波器可以分为有源和无源滤波器。有源滤波器的设计引入了有源元件—集成运算放大器,由于运算放大器具有近似理想的特性,且可以省去电感,因此可以得到接近理论预测的频响应特性,并能减小体积。但由于受到运放带宽的限制,有源滤波器的滤波频带一般不很高。[38]无源滤波器采用分立元件进行设计,其频率范围比较宽,因此一般用于高频设计。低通滤波器可以分为巴特沃什滤波、切比雪夫滤波、贝赛尔滤波和椭圆滤波等。特沃什低通滤波器的通带和阻带都是平坦的,但是其过渡带太过平缓;切比雪夫低通滤器的通带是等波纹抖动的,阻带是平坦的,过渡带比巴特沃什稍陡;贝赛尔低通滤波器切比雪夫低通刚好相反,通带平坦,阻带是等波纹抖动的;椭圆低通滤波器的通带和阻都是抖动的,但是其过渡带下降迅速,过渡带很窄。[39]在本系统中,采用了具有较窄过渡带特性的椭圆滤波器,并采用7阶椭圆低通滤波。根据系统要求输出信号的频率可达60MHz,设定其通带为60MHz,且7阶滤波具有下降速度更快的过渡带,可以有效的滤除1OOMHz以上的高频干扰。考虑到实际的椭圆滤波器的设计与理论分析是有所不同的,在本设计中采用理论分析与测量滤波器的实际频谱特性相结合的方法,在实际的调试中逐渐改变滤波器的元件值,以使频谱特性达到最佳。首先,按照低通椭圆滤波器的理论设计方法,采用查归一化滤波器手册的方法设计出原始的7阶椭圆低通滤波器,初步确定元件值。22基于DDS的高精度信号发生器的设计已知要求从0到60兆赫的衰减不大于0.2分贝,而100兆赫以上衰减大于75分贝。计算出选择因数为:ΩS=WS/WC=fs/fc=100/60=1.667(3.1)查椭圆函数滤波器的归一化元件值表,选n=7,p=20%(相应Ar=0.177分贝),Qs=1.667,此时As=76.62分贝,指标均能满足,且有富余。查得归一化参数后,应用综合标定公式C=1/wcRLC(3.2)计算出实际元件值。其次,对理论滤波器进行改进。由于电容和电感元件的特性并不是理想的,这一点在高频中尤其突出,所以需要改进。在实际设计中,在PCB板上把滤波器连接好,用频率特性测试仪对连接好的滤波器进行测量,如果幅频特性不好,则调整电容的值,再次测量滤波器的幅频特性,如此反复,直到该滤波器的特性满足要求为止。经过实验调整,该7阶椭圆低通滤波器的电路参数如图3.5所示。在Protel中进行滤波器特性仿真,得到特性曲线如图3.6所示。图3.5低通滤波器的电路图图3.6低通滤波器的特性曲线23陕西科技大学毕业设计说明书3.6本章小结本章详细介绍了AT89C52和DDS芯片AD9851,并说明了它们的连接,接下来介绍了显示模块的电路,最后详细分析了低通滤波器的设计过程。通过这章完成了硬件的设计。24基于DDS的高精度信号发生器的设计4软件实现系统监控程序是控制单片机系统按照预定操作方式运转的程序,是整个系统程序的框架。在本系统中,单片机的主要任务是在操作者按下不同的按键后,执行相应的任务,各个任务执行的先后顺序取决于键码。根据这样的功能和操作方法,程序总体结构采用键码分析作业调度型,即作业调度完全服从操作者的意图,操作者通过键盘发出作业调度命令,监控程序接收到控制命令后,通过分析启动对应的作业。系统软件设计采用模块化设计[48]的方法,它是把一个功能完整的较大的程序分解为若干个功能相对独立的较小的程序模块,对各个程序模块分别进行设计、编程和调试,最后把各个调试好的程序模块联成一个大的程序。模块化程序设计的优点是单个功能明确设计和调试比较方便、容易完成。一个模块可以为多个程序所共享。模块化编程的具体体现是把各个功能相对独立的模块作为子函数,主程序是一个不断循环检测结构。当系统上电自检、初始化后,进入信号输出的循环,并自动查询面板按键的状态,以检测用户可能输入的指令,确定程序将要执行的功能。在系统工作中,串行口是一种非常方便可行的通讯方式,PC机可以通过串行口向本系统发出命令[28]。本系统软件由主监控程序模块、键盘扫描模块频率控制字的送入模块、数码管显示模块构成。其中主监控程序是系统软件的主程序,是整个系统软件的核心,上电复位后系统首先进入监控主程序。它的任务是识别命令、解释命令,并获得完成该命令的相应模块的入口,起着引导仪器进入正常工作状态,协调各部分软件有条不紊地工作的重要作用[29]。25陕西科技大学毕业设计说明书4.1主监控程序模块程序开始后,运行初始化程序,包括初始化单片机AT89C52、初始化AD9851、初始化LED显示模块等。然后扫描键盘状态,检查到有键按下就运行键值处理程序,对按键值进行查表处理,然后执行相应的子程序。输入的信号相关信息通过运行LED显示程序,在数码管上显示正确的输入数据和提示字符。在按下执行键后,AT89C52计算出所需信号的数据或控制命令,将其传送到AD9851,输出最终信号。接下来返回主程序,继续扫描键盘,等待下一次命令的输入[30]。初始化程序完成具体工作如下:1.设置PSW的RSO,RS1均为0,选择第一组寄存器作为当前工作寄存器。2.设置堆栈指针SP=70H。3.调用LED初始化程序。4.设置30H为键盘输入值存放区。5.初始化并行口通信,允许并行口中断,允许定时器0中断。6.转键盘扫描程序系统主监控程序框图如图4.1所示。对AD9851进行初始化控制时,对AD9851写入控制字。一旦设定后,AD9851将保持设定状态不变,直到重新进行设置[31]。26基于DDS的高精度信号发生器的设计图4.1系统主监控程序流程4.2键盘扫描模块4.2.1键盘简述单片机使用的键盘分为独立式和矩阵式两种。本系统采用矩阵式键盘。键盘采用标准44键盘,除了0~9的10个数字键外,还有小数点,删除键和菜单键等。其分布图如图4.2所示。其结构如图4.3所示:图4.2矩阵式键盘外观分布图图4.3行列式键盘结构图矩阵键盘又称行列式键盘,它是利用4条I/O线作为列线组成的键盘。在行线和列线的每一个交叉点上,设置一个按键。这样键盘中的按键的个数就是44个这种行列式键盘结构。能够有效地利提高单片机系统中I/O口的利用率。图4.3为矩阵键27陕西科技大学毕业设计说明书盘的结构图,行线接P0.4~P0.7,列线接P0.0~P0.3,行线另一端悬空,列线的另外一端通过上拉电阻与+5V电源相连。当某一个按键按下时,该键所连接的行线和列线接通时端口产生低电平0[32]。4.2.244矩阵键盘的编程方法(a)先读取键盘的状态,得到按键的特征编码。先从P0口的高四位输出低电平,低四位输出高电平,从P0口的低四位读取键盘状态。再从P0口的低四位输出低电平,高四位输出高电平,从P0口的高四位读取键盘状态。将两次读取的结果结合起来就可以得到当前按键的特征编码。使用上述方法我们得到16个建的特征编码。举例说明如何得到按键的特征编码:假设2键被按下,找其按键的特征编码。从P0口的高四位输出低电平,即P0.4~P0.7为数输出口,低四位输出高电平,即P0.0~P0.3为输入口。读P0口的低四位状态为1101,其值为0DH。再从P0口的高四位输出高电平,即P0.4~P0.7为输入口,低四位输出低电平,即P0.0~P0.3为输出口。读P0口的高四位状态为1110,其值为E0H。将两次读出的P0口状态值进行逻辑或运算就得到其按键的特征编码为EDH。用同样的方法可以得到其它15个按键的特征编码。(b)根据按键的特征编码,查表得到按键的顺序编码。将用上述方法得到的16个按键的特征编码按图2按键排列的顺序排成一张特征编码与顺序编码的对应关系表,然后用当前读得的特征编码来查表,当表中有该特征编码时,它所在的位置就是对应的顺序编码。(c)矩阵键盘按键值查找程序的具体编程这个演示程序的具体功能有:(a)识别键盘有无按键按下,若无建就返回。28基于DDS的高精度信号发生器的设计(b)如果有按键按下,找出具体的按键值(顺序码)。矩阵键盘按键查找程序键值存入30H单元KEY-SCAN:;识别键盘有无键按下子程序MOVP0,#0F0H;置列线为0,行线为1MOVA,P0;读P0口ANLA,#0F0H;读取高四位MOVB,A;暂存到BMOVP1,#0FH;置列线为1,行线为0MOVA,P0;读P0口ANLA,#0FH;读取低四位ORLA,B;将高四位与低四位逻辑或运算重新组合CJNEA,#0FFH,KEY-IN1;0FFH为无按键按下RETKEY-IN1:;识别具体按键值子程序MOVB,A;将按键的特征编码暂存与BMOVDPTR,#KEYABLEMOVR3,#0FFHKEY-IN2:INCR3;顺序码加1MOVA,R3MOVCA,@A+DPTR;查表CJNEA,B,KEY-IN3;比较,若相同则找到按键的特征编码MOVA,R3;找到特征编码后,取顺序码MOV30H,A;存入30H单元RETKEY-IN3:29陕西科技大学毕业设计说明书CJNEA,#00H,KEY-IN2;未完继续查RET;00H为结束码;特征编码与顺序编码的对应关系KEY-TABLE:DB0EEH,0EDH,0EBH,0E7H,0DEH;1,2,3,4,5,顺序码DB0DDH,0DBH,0D7H,0BEH,0BDH;6,7,8,9,0,顺序码DB0BBH,0B7H,07EH,07DH,07BH,077H;∙,TAB,←,→,DEL,EXE,顺序码DB00H;顺序码4.3频率控制字的送入模块通过单片机P1口将40位的数据传输AD9851,由于并行传输一次只能送八位,所以要通过编程分5次将其送入,其中单片机的P3.0口分别与AD9851的FQ-UD和W-CLK连接,在第一个W-CLK上升沿装入8位数据,并把指针向下一个输入寄存器,连续5个W-CLK上升沿后,W-CLK的边沿就不再起作用,直到复位信号或FQ-UD上升沿把40位数据从输入寄存器输入道频率、相位数据寄存器,从而更新DDS输出频率和相位,同时把地址指针复位到第一个数据寄存器[33]。并列传输程序:40位数据已存放在7FH~76H中:MOVR0,#7FH;设置计数器CLRP3.0;将W-CLK置低CLRP3.1;将FQ-UD置低MOVTOMD,#21H;定时器0,方式1MOVTH0,#0FFH;定时间隔10uSMOVTL0,#0FBHSETBTR0;启动定时器30基于DDS的高精度信号发生器的设计SETBET0;开定时器0中断SETBEA;开总体中断AJMP¥;就地循环等待中断T0F:CLRTR0;关闭定时器MOVTH0,#0FFH;重新赋值MOVTL0,#0FBHMOVP1,@R0;取出要传送的八位数据DECR0;再取下一个CJNER0,#74H,LL3;判断是否送完,75H中放的是最高8位,未送完转到LL3SETBTR0;启动定时器CPLP3.1;FQ-UD置高MOVR0,#7FH;循环传送40位数据AJMPLL4LL3:SETBTR0CPLP3.0;输出周期为20uS的脉冲CLRP3.1;保证FQ-UD为低LL4:RETI4.4数码管显示程序的编程方法数码管不同位显示的时间隔可以通过调整延时程序的延时长短来完成[34]。数码管显示的时间间隔也能够确定数码管显示时的亮度,若显示的时间过长,显示时数码管的亮度将亮些,若显示的时间间隔短,显示时数码管的亮度将暗些。若显示的时间间隔过长的话,数码管显示时将产生闪烁现象。所以,在调整显示的时间间隔时,即要考虑到显示时数码管的亮度,又要数码管显示时产生闪烁现象[35]。根据要使用的数码管的具体位置来确定扫描初值和扫描方向,31陕西科技大学毕业设计说明书根据使用数码管的个数来确定扫描的个数。准备好要显示的数据,放入相应的显示单元中。5位数码管显示子程序;从左到右一次点亮8个数码管DIPLAY:MOVR1,#07FH;扫描初值送入R1MOVR2,#08H;扫描位数送入R2MOVR0,#30H;开始填充显示单元DIP1:MOVA,@R0;显示内容送入AMOVDPTR,#TABLE;获得表头MOVCA,@A+DPTR;查表获得显示数据MOVP2,A;显示单元数据MOVP3,R1;开始显示当前位MOVA,R1;准备显示下一位RRAMOVR1,AINCR0;取下一个单元地址LCALLDELAY2MS;延时2MSDJNZR2,DISPI;重复显示下一个RET;显示完成,返回因键值显示只需用一位数码管可将上面的显示程序进行优化,得到下面的显示程序键值显示子程序KEY-PLAER:MOVA,30H;键值数据送入AMOVDPTR,#TABLE;取段码表地址MOVCA,@A+DPTR;查显示数据对应段码MOVP2,A;段码送入P0口CLRP3.7;第一个数码管显示CALLDELAY2MSSETBP3.7RETTABLE:32基于DDS的高精度信号发生器的设计DB0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90H;1~04.5本章小结本章分四部分介绍了本系统的软件部分,首先简单介绍了本系统的整体软件设计,在设计了三个子程序,即键盘扫描部分、显示部分和数据传入DDS芯片部分。这样通过人的控制一起来实现信号的产生。33陕西科技大学毕业设计说明书5结束语本课题耗时半年多时间,最终完成了任务,达到了各项指标要求。在这工程中,熟悉了对protel99SE的使用,对电路设计和编程也有了更深入的熟悉,最重要的是使我明白了一个真正的设计的过程,一个真正的设计需要严谨的态度。实际应用表明DDS技术是可以应用到高精度信号发生器中的,特别是在对频率切换速度、频率分辨率、相噪和杂散要求比较高的场合,DDS技术显示了特殊的优势。本文只是对DDS的系统进行了初步的研究,要达到性能完善,还有很多工作要做。比如电磁兼容的问题、滤波器的优化问题、功耗问题、体积问题和性能稳定性问题、安装问题等等,这些问题还需要近一步的完善,这样才能获得更佳的整体性能。34基于DDS的高精度信号发生器的设计致谢论文即将完成之际,我首先衷心感谢我的导师李春霞老师。李老师以其严谨的治学态度、广博的知识、扎实的学术功底和敏锐的学术洞察力深深地影响着我。他深厚的理论功底和丰富的实践经验对我课题的完成起到了至关重要的作用,同时对我今后从事技术开发工作来说,这也是一笔难得的财富。我是一个积极性差的同学,每次都是李老师督促我做毕业设计,没有李老师的督促,就没有我的毕业设计的完成。在此,特向李老师致以深深的敬意和由衷的感谢。感谢朝夕相处的同学们,他们给护了我诸多的鼓励、热情的的帮助,给我提出了许多的宝贵意见和建议。深深感谢我的家人多年来在生活、学习中给我无微不至的关怀和支持,是他们的爱使得我能顺利完成学业。35陕西科技大学毕业设计说明书参考文献[1]郭荣祥,郭吉祥.AD9850125MHzDDS频率合成器的原理及应用.电子技术应用,1997(12):65-68.[2]HenryT.Nicholas,lllandHenrySamueli.AnAnalysisoftheOutputpectrumofDirectDigitalFrequencySynthesizerinthePresenceofPhase-AccumulatorTrUncatIOn.IEEE41st.AnnualFreqrencyControlSymposium,1987:495-502.[3]许慧波,张厥盛.直接数字频率合成DDS综述.电子科技杂志,1992,(4):1-7.[4]蒋焕文.直接数字频率合成器的噪声分析.北方交通大学学报,1987(4):55-63.[5]高望.直接数字频率合成技术及其杂散分析.南京理工大学硕博士学位论文,2002.[6]乐翔,秦十.直接数字频率合成信号的杂散性能分析.清华大学学报(白然科学版),2000,1.[7]下建新.直接数字频率合成中的相位截断误差分析.电子测量与仪29学报,1997,(4):1-6.[8]郭金维,汤汉屏.DDS技术浅析.数据通信,2002(3):50-52.36基于DDS的高精度信号发生器的设计[9]李衍忠,蔡英杰等.DDS谱质分析及其杂散抑制研究综述.现代雷达,2000,No.4.[10]吴国利,汤汉屏.一种抑制DDS杂散的方法.空军电讯工程学院学报,1999,No.2.[11]刘益成,罗维炳.信号处理与过抽样转换器.北京:电子工业出版社,1997.[12]童诗白,华成英.模拟电子技术基础(第二版).北京:高等教育出版社,2001.1.[13]常晓明.Verilog-HDL实践与应用系统设计.北京:北京航空航天大学出版社,2003.1.[14]李书浩,仇广煜等.数字逻辑应用与设计.北京:机械工业出版社,2000.[15]沈树华等.DDS—一种新型频率合成技术(一).通信与广播电视,1995(3):24-27.[16]胡广书.数字信号处理—理论、算法与实现(第三版).清华大学出版社,2003.8.[17]程佩青.数字信号处理教程.清华人学出版社,2001.8.[18]张志涌.精通MATLAB6.5版.北京:北京航空航天大学出版社,2003.3.[19]梁虹,梁洁,陈跃斌.信号与系统分析及MATLAB实现.北京:电子工业出版社,2002.2.[20]张玉兴,彭清泉.DDS的背景杂散信号分析.电子科技人学学报,1997,26(4):362-365.[21]包明,赵明富,陈渝光.EDA技术与数字系统设计.北京:北京航空航天大学出版社,2002.7.[22]邱腾禄.FPGA.DDS理论研究及在电子技术教学实验中的应用.西北工业大学硕十学位论文,2001.3.[23]宋万杰,罗丰,吴顺君.CPLD技术及其应用.西安:西安电子科技大学出版社,1999.9.[24]杨吉斌.数字系统设计与VerilogHDL.北京:电子工业出版社,2002.1.[25]干幸之等.AT89系列单片机原理与接口技术.北京:北京航空航天大学出版社,2004.5.37陕西科技大学毕业设计说明书[26]李广第,朱月秀,干秀山.单片机基础(修订本).比京:北京航天航空大学出版社,2004.1.[27]干道宪.CPLD/FPGA可编程逻辑器件应用与开发.北京:国防工业出版社,2004.1.[28]胡汉才.单片机原理及其接口技术.北京:清华大学出版社,2004.2.[29]徐爱钧,彭秀华.单片机高级语言C51Windows环境编程与应用.北京:电子工业出版社,2001.7.[30]何立民.单片机高级教程—应用与设计.北京:北京航空航天大学出版社,2000.8.[31]李建忠.单片机原理及应用.西安:西安电子科技大学出版社,2002.2.[32]李辉.ISP系统设计技术入门与应用.北京:电子工业出版社,2002.2.[33]夏字闻.Verilog数字系统设计教程.北京:北京航空航天大学出版社,2003.7.[34]范分强,兰蝉丽.单片机语言C51应用实战集锦.北京:电子工业出版社,2003.3.[35]马忠梅等.单片机的C语言应用程序设计.北京:北京航空航大人学出版社,2003.11.38基于DDS的高精度信号发生器的设计附录附图Ⅲ-1系统的PCB图39',)

提供基于DDS的高精度信号发生器的设计会员下载,编号:1700817705,格式为 docx,文件大小为43页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载