基于FPGA的HDMI转SDI设计与实现

本作品内容为基于FPGA的HDMI转SDI设计与实现,格式为 docx ,大小 319668 KB ,页数为 7页

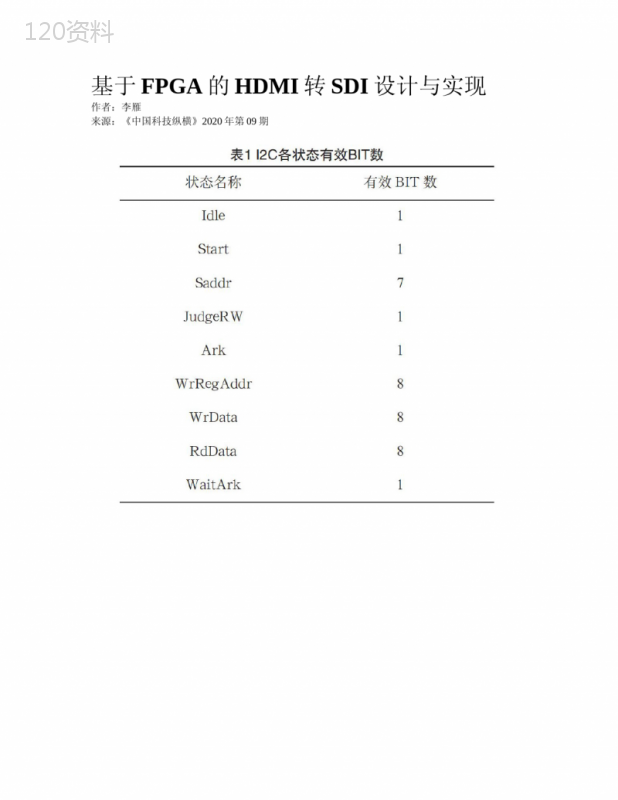

('基于FPGA的HDMI转SDI设计与实现作者:李雁来源:《中国科技纵横》2020年第09期摘要:介绍了HDMI2.0的协议及通过FPGA编码实现HDMI协议的DDC、解扰、解码、音频包提取、视频数据提取的功能。使用IPSMPTEUHD-SDI和UHDSDIAudio实现SDI协议,自编接口适配程序完成SDI音频嵌入接口实现以及SDI视频DS流成帧器的实现。关键词:HDMI;SDI;IEC60958;EDID;I2C;HPD中图分类号:TN948.6文献标识码:A文章编号:1671-2064(2020)09-0062-030引言高清晰多媒体接口HDMI已经成为任何高清数字电视和多媒体设备之间的标准接口,目前广泛应用在数字液晶电视、数码相机、家用投影机、机顶盒、平板电脑等消费类电子中。在专业的数字电影投影机领域,串行数字接口SDI作为专业广播室视频设备中的数据传输接口,通过同轴电缆传输无压缩的数字视频信号,保证画质无损。由于SDI接口的硬件成本比较高昂,且信号传输的数据量大,对信号质量要求度比较高,所以只有在一些专业的音视频设备中才具有SDI接口,但由于一系列消费类电子产品目前已经能支持清晰度质量高的HDMI信号输出,为了实现HDMI信号能够输出到具有SDI接口的设备中进行处理,所以需要进行HDMI转SDI的信号转换[1]。1FPGA内部实现架构FPGA采用XILINX公司的XCKU035-FBVA676-2,该芯片的GTH高速串行收发器能支持12GSDI所需的11.88G速率,在接收端,HDP模块上电后输出高电平,使得源端检测到HDMI在线,然后源端通过I2C访问FPGA内部的EDID,获取FPGA作为HDMI接收端的接收能力,例如分辨率,刷新率等,从而源端发送最适合接收端的视频源数据。3路5.94G的HDMI信号CH0/1/2进入FPGA的GTH,GTH主要完成时钟恢复,串并转换,得到40bit位宽的并行数据输出,对原始数据进行解扰后,识别出控制周期,数据岛周期,视频数据周期。从视频数据周期数据提取出HS,VS,DEN,DATA,从数据岛周期提取出AES格式音频数据。HDMI接收到的视频数据一般为RBG格式,转换成SDI的YCbCr格式后缓存,SDI成帧器根据前级数据的HS,VS,DEN产生行列计数及相应的前导数据,将YCbCr数据取出填充到帧结构的数据中形成DS数据流,使用XILINX的IPCORESMPTEUHD-SDI完成12G-SDI信号合成,首先是在DS数据流中插入ST352,输出的DS流进入XILINX的IPCOREUHDSDIAudio,该IP可以将音频数据通过AXIS接口插入到DS中,插入音频数据的DS再接回SMPTEUHD-SDI的DS_IN,形成40bit的并行数据后通过GTH发送出12G-SDI。模块端内部框图如图1所示。2FPGA内部详细设计2.1HPDHDP是HDMI的热插拔功能,当HDMI线缆没有插入或者FPGA没有上电的时候,该信号是0V,FPGA上电后固定输出高电平,经过硬件器件变为5V,插上HDMI线缆后,源端就能检测到HDMI从机在线。2.2EDIDEDID是源端通过I2C读取从机ROM,获取从机接收能力,从而发送相应的数据源。I2C的设计遵循I2C的标准协议。使用本地晶振25M作为系统时钟,该时钟远大于400k的I2C速率,方便准确采集I2C的时钟和数据边沿以及判断时钟高电平的中间时刻。使用状态机进行从机设计,划分9个状态,分别是Idle(空闲),Start(开始),Saddr(从机地址),JudgeRW(读写判断),Ark(应答),WrRegAddr(写寄存器地址),WrData(写数据),RdData(读数据),WaitArk(等待应答)。状态跳转规则要符合I2C标准协议。在时钟高电平时检测到数据出现下降沿,强制进入Start状态,在时钟高电平时检测到数据上升沿,强制进入Idle状态。每次检测到时钟高电平中间时刻,对状态进行BIT计数,每次转换状态,BIT计数归零。达到状态预设的BIT值时,状态跳变。各个状态对应的BIT计数值如表1所示。在WrRegAddr状态,记录主机要访问的寄存器,在WaitArk状态,检测到主机应答后,寄存器地址自动+1。从而支持连续读模式。在WaitArk状态,根据寄存器地址将相应数据寄存到输出移位寄存器,移位寄存器在时钟高电平时刻将数据移位输出,完成I2C的數据传输。2.3HDMI解扰HDMI2.0版标准中定义了非加扰控制周期,占用8个时钟周期,用于三个数据通道的同步对齐及复位加扰因子为初始值。加扰算法的线性反馈移位多项式为G(x)=1+x11+x12+x13+x16。数据通道0的初始值为0xFFFF,数据通道1的初始值为0xFFFE,数据通道2的初始值为0xFFFD。当接收器状态为视频数据周期时,将8bit视频数据与解扰因子的高8bit进行异或运算,得到解扰后的视频数据。当接收器状态为数据岛周期时,将4bit音频及辅助数据与解扰因子的高4bit进行异或运算,得到解扰后的音频及辅助数据。当接收器状态为加扰控制周期时,将4bit控制矢量与解扰因子的高4bit进行异或运算,得到控制数据[2]。2.4信号段检测数据解扰后,需要识别出控制周期,数据岛周期,视频数据周期。识别的特征数据在HDMI2.0中,与以前的版本略有不同,不同之处在于:(1)视频数据周期保护带,HDMI2.0采用的是视频数据编码,而HDMI1.4采用的是固定值;(2)数据岛周期保护带,HDMI2.0通道0采用的是可纠错编码,通道1和2采用的是视频数据编码,而HDMI1.4采用的是固定值;(3)控制周期,HDMI2.0中非加扰控制周期采用控制周期编码,加扰控制周期采用查找表,而HDMI1.4只采用控制周期编码。根据各个周期的特征数据完成识别后,生成特征标致信号给后级模块[3]。2.5视频接收从CH0中提取出HS,VS,在控制周期,HS,VS采用CTL编码。在数据岛周期,采用TERC4编码。视频数据使用TMDS编码。CTL编码和TERC4编码分别又4种情况和16种情况,采用查找表完成,TMDS解码根据协议中的解码流图进行设计。最高位为1时,低8位取反,否则保持不变,得到解码中间数据。次高位为1时,解码的bit[i]=解码中间数据的bit[i]异或解码中间数据的bit[i-1]。次高位为0时,解码的bit[i]=解码中间数据的bit[i]异或解码中间数据的bit[i-1]后取反。上述操作i=7到1。解码的bit[0]=解码中间数据的bit[0]。2.6音频接收音频数据位于数据岛周期中,数据岛周期除了传递音频包,还可以传递各种控制包,在本次设计中,我们只提取数据岛周期包类型值为0x02的音频采样包。首先数据先进行TERC4解码,得到4bit的原始数据。每次数据岛周期持续时间为32个时钟周期的整数倍。连续32个CH0的bit[2]组合得到4个包头字节,其中前三个字节是内容,最后一个字节是BCH(32,24)编码后的校验位。通过BCH解码能够实现序列的误码探测和误码纠错,最多可纠正4个bit错误。我们需要提取第一字节为0x02的音频采样包,第二字节的bit[4]为0表示音频包中有2个音频通道,为1表示音频包中有8个音频通道。当2通道时,子包0/1/2/3分别传递音频采样channel0/1的采样点N,N+1,N+2,N+3。当8通道时,子包0/1/2/3分别传递音频采样channel0~7的采样点N。第二字节的bit[30]∶表示音频通道有效。第三字节的bit[3:0]在音频通道有效的条件下,为1表示该通道此包的音频采样点是填充数据,解码时应当删除该填充采样点。第三字节的bit[74]∶各个bit为1时分别代表每个音频通道对此时时IEC60958的帧头第一个音频采样点。用于设置PCUV的帧同步计数器归零。CH1和CH2的bit位按一定规律结合成4个子包,每个子包有7个有效字节,1个字节的BCH(64,56)校验位,能够检测错误并纠正最多4个bit的错误。bit组合规则是CH1和CH2的bit[N]交叉组合得到子包N。每个子包的内部结構相同。字节0~2传递IEC60958的子帧0的bit[274]∶,也就是左声道音频采样,字节3~5传递IEC60958的子帧1的bit[274]∶,也就是右声道音频采样,字节6的bit[30]∶和[74]∶传递IEC60958子帧0和1的bit[30]∶,即PCUV。P为校验位,C为状态位,U为用户定义位,V为有效指示位。其中192个C组成一个控制帧,指示音频的采样速率,有效位等信息。FPGA内收到前级的数据岛周期指示信号后启动数据计数器,每次计数到32的整数倍产生一个收包完成信号,在计数的同时,对CH1/2的数据bit[30]∶,CH0的bit[2]分别进行移位寄存。得到9组32bit的数据。收包完成信号有效时,按照前面所述的bit排列规则组合得到包头和子包,同时启动步骤计数器,分步对数据包进行解析。由于有可能出现连续两个数据岛周期,所以必须在32个步骤内完成解析。在步骤0判断包头第一个字节是0x02,产生音频包指示信号,有效期设定为16个时钟,则说明设计在16个步骤内完成解析。在步骤1解析出通道有效和通道填充位以及IEC60958的帧起始标致。在步骤2~9中,分别解析出4个子包中的8个音频采样点和对应通道号以及相应的PCUV。2.7RGB转YCbCrHDMI一般默认传递的是RGB信号,这是协议中要求必须支持的视频格式,SDI传递的则是YCbCr格式的视频数据,因此两者之间需要进行格式转换。实现公式如下:Y=0.299R+0.587G+0.114BCb=-0.1687R-0.3313G+0.5BCr=0.5R-0.4187G-0.0813BFPGA中的乘法位宽位18位,本次设计实现采用Q16实现,转换后的公式为:Y=19595R+38470G+7471BCb=-11056R-21712G+32768BCr=32768R-27440G-5328B得到的结果右移16位即可。转换的结果需存入8个缓存,以便生成12G-SDI的8个DS流。奇数行的采样点Y0,1存入DS1,采样点Y3,4存入DS3,依次逐个存入DS1,3。奇数行的采样点Cb0,Cr1,存入DS2,采样点Cb2,Cr3存入DS4。依次逐个存入DS2,4。偶数行的采样点Y0,1存入DS5,采样点Y3,4存入DS7,依次逐个存入DS5,7。偶数行的采样点Cb0,Cr1,存入DS6,采样点Cb2,Cr3存入DS8,依次逐个存入DS6,8。2.8SDI音频缓存HDMI解码的音频数据格式与SDI是基本一致的,只需将IEC60958的子帧0帧头指示标志转译成0x1,其余子帧0标志转译成0x2,所有子帧1标志转译成0x3即可和PCUV,音频数据一起组合成32bit存入音频缓存,使用AXIS接口的缓存,AXIS入口的ID信号继续使用前级的TID表示通道号。当后级有效后,写使能置1,从而才能将前级音频数据写入缓存。写入缓存达到缓存量的一半时,读使能置1,FPGA内部对主时钟进行分频计数得到48kHz的读时钟使能,在该使能的作用下,产生通道有效计数器,将输出给后级AXIS的valid信号拉高,当后级AXIS接口的ready信号有效时,通道计数器加1,当通道计数器的值大于设定的N通道时,valid信号拉低。结束本次采样使能的AXIS传输。当AXIS的valid和ready都有效时,产生AXIS缓存Master接口的ready,更新下一个通道数据。2.9SDI帧产生当HDMI接收的VS由低到高时,表明一个图像帧的开始,设置行列计数器,由于12G-SDI由4个1920X1080的子图像组成,根据视频格式协议,1920X1080P的列计数为2200个时钟周期,行计数为1125行。42到1121行传递有效视频数据,每行的最后1920个时钟周期传递有效数据。SDI每行的0~2字节和276~278字节分别输出前导0x3FF,0x000,0x000.第3字节为EAV字段,在42到1121行为0x274,其余行为0x2d8,第279字节为SAV字段,42到1121行为0x200,其余行为0x2ac。数据字段从前级8个缓存读取数据,形成8路DS流。2.10SMPTEUHD-SDI在IPCatalog里选择SMPTEUHD-SDI,将MaximumLineRate设置为12GSDI8DS,勾选InsertST352inC-Stream,因为12G-SDI的C码流中要求插入ST352。插入ST352后的DS流tx_ds1_st352_out输出给音频嵌入模块。音频嵌入模块嵌入的数据接到tx_ds1_anc_in接口,tx_use_anc_in设置为1,选择tx_ds1_anc_in接口的DS流给IP后级,最终产生嵌入音频的并行40bit输出,接到GTH进行并串转换,生成12G-SDI信号。2.11UHDSDIAudio(Embed)在IPCatalog里选择SMPTEUHD-SDI,AudioFunction选择Embed时为辅助数据嵌入功能,UHD-SDIStandard設置为12GSDI8DS,MaxmumAudioChannels设置为8,因为HDMI能支持8路音频。不勾选EnableAxiLiteInterface,因为我们使用接口直接配置模式。插入音频后的DS流输出给SMPTEUHD-SDI的tx_ds1_anc_in接口。3结语本次通过FPGA实现HDMI2.0的接收以及12G-SDI的发送,对HDMI的协议部分内容进行了分解分析,整个HDMI2.0是个非常丰富的标准,可以支持多种视频分辨率和刷新率,以及多种不同的音频格式。本次设计解析了最常见的音频格式以及12G-SDI能传输的最大速率视频。参考文献[1]黄荣铭.基于FPGA的4KHDMI至12G-SDI信号格式转换技术的研究与设计[D].福州:福州大学,2018.[2]魏国.基于HDMI2.0的加解扰器设计[J].电子技术,2018(3):52-55.[3]魏国.一种基于HDMI2.0的编解码器设计[J].电子技术应用,2018,44(6):19-22.',)

提供基于FPGA的HDMI转SDI设计与实现会员下载,编号:1700877853,格式为 docx,文件大小为7页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载