基于FPGA的SATA控制器介绍v1

本作品内容为基于FPGA的SATA控制器介绍v1,格式为 doc ,大小 8036904 KB ,页数为 9页

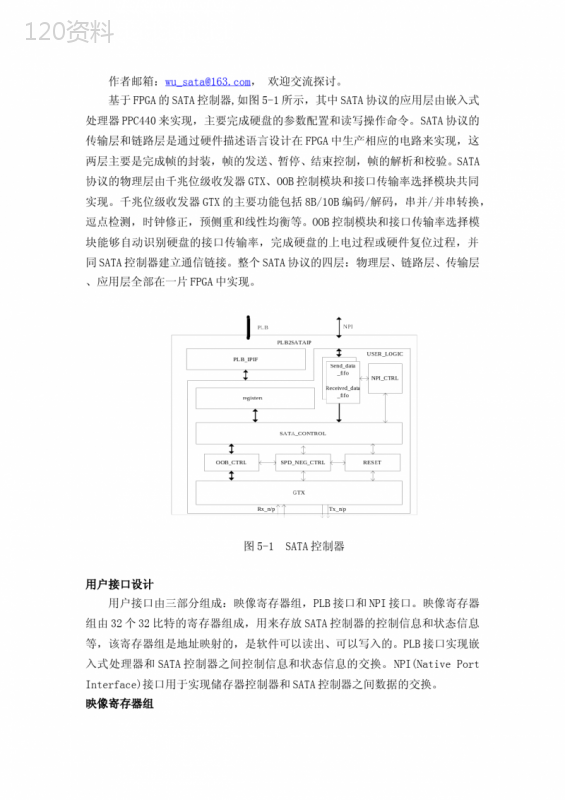

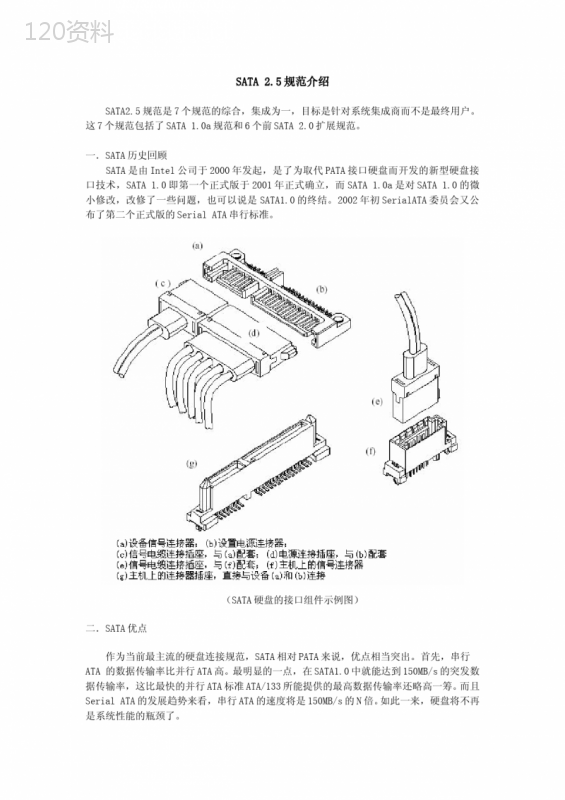

('作者邮箱:wu_sata@163.com,欢迎交流探讨。基于FPGA的SATA控制器,如图5-1所示,其中SATA协议的应用层由嵌入式处理器PPC440来实现,主要完成硬盘的参数配置和读写操作命令。SATA协议的传输层和链路层是通过硬件描述语言设计在FPGA中生产相应的电路来实现,这两层主要是完成帧的封装,帧的发送、暂停、结束控制,帧的解析和校验。SATA协议的物理层由千兆位级收发器GTX、OOB控制模块和接口传输率选择模块共同实现。千兆位级收发器GTX的主要功能包括8B/10B编码/解码,串并/并串转换,逗点检测,时钟修正,预侧重和线性均衡等。OOB控制模块和接口传输率选择模块能够自动识别硬盘的接口传输率,完成硬盘的上电过程或硬件复位过程,并同SATA控制器建立通信链接。整个SATA协议的四层:物理层、链路层、传输层、应用层全部在一片FPGA中实现。图5-1SATA控制器用户接口设计用户接口由三部分组成:映像寄存器组,PLB接口和NPI接口。映像寄存器组由32个32比特的寄存器组成,用来存放SATA控制器的控制信息和状态信息等,该寄存器组是地址映射的,是软件可以读出、可以写入的。PLB接口实现嵌入式处理器和SATA控制器之间控制信息和状态信息的交换。NPI(NativePortInterface)接口用于实现储存器控制器和SATA控制器之间数据的交换。映像寄存器组应用层提供一个映像寄存器组,处理器传输各种命令时,向映像寄存器中写入命令或读取状态信息,设备通过发送帧来更新映像寄存器,对主机的命令进行响应。在SATA协议中定义了有关映像寄存器组中寄存器的类型与用途。本设计中寄存器组由32个寄存器组成,其中有5个寄存器是用户自定义的,其余的兼容ATA协议指令集,包括Status、Command、Error、Feature,LBAlow等。5个用户自定义的寄存器用于对SATA控制器中某些模块进行复位、观察状态和调试信息以及参数配置等。其余寄存器用于存放SATA_CONTROL的控制信息、状态信息、LBA地址和参数等。寄存器组的一端与PLB总线相连,用于PPC通过PLB读/写寄存器组,另外一端与SATA_CONTROL模块相连,SATA_CONTROL模块通过该端口读/写寄存器组。PLB接口PLB总线是一种高带宽、低延迟、高性能的处理器内部总线,用于连接高性能CPU、高速存储器控制器、仲裁器、高速的DMA控制器等高性能、大宽带的片上设备。PLB总线架构是由IBM开发的,Xilinx公司获得IBM公司的许可,在其产品上使用PLB总线。由于PLB总线协议信号很多,较为复杂,为了让用户更加方便的使用、加快开发进度,XILINX公司为用户开发了PLB生成向导。该向导自动生成PLB总线与用户逻辑之间的接口,即IPIF(IPInterface)。利用IPIF解决PLB总线接口和用户逻辑接口之间的转换。在用户逻辑看来,PLB接口表现为简单IPIC(IPInterconn-ect)接口。用户使用该向导还可以根据需要选择相应的模块和功能[57]。采用PLB总线作为用户接口可以使SATA控制器应用范围更加广泛,用户只需要通过PLB总线对映像寄存器进行配置就可以实现SATA控制器的功能。本设计中PLB总线只是用于传递少量的参数和状态信息,因此,PLB模块配置成了从(slave)设备,以节约FPGA资源。核心模块SLAVEAttachment提供了PLB从设备的基本功能,它在PLB总线和IPIC之间执行协议和时序的转换。NPI接口SATA控制器读写的数据都不经过PLB总线,而是通过NPI接口与多端口储存器控制器(MPMC)相连,直接读写存储单元。避免了由于PLB的竞争和冲突导致有效带宽小、利用率低的情况。这样的设计具有很强的实时性,数据传输带宽高NPI接口控制器(NPI_CTRL)用于实现NPI接口协议,数据宽度为64位,支持burst工作模式,一次burst读或写最多可以传输256个字节数据,每次burst之后硬件会自动更新地址,得到下一个burst的起始地址。发送数据时,NPI接口控制器(NPI_CTRL)根据命令和配置信息从存储单元(DDR2内存条)中指定的起始地址处读取指定数量的数据到发送数据缓冲区(send_data_fifo),然后由SATA控制器将数据发送给硬盘;接收数据时,SATA控制器先将接收的数据写入接收数据缓冲区(received_data_fifo),然后由NPI接口控制器(NPI_CTRL)根据命令和配置信息将数据写入存储单元(DDR2内存条)中指定起始地址处。SATA控制器的综合与实现SATA控制器的开发是在XILINX公司的ISE集成开发环境中进行的,版本号为10.1.3。并且使用XILINX公司提供的综合,编译,布局布线等工具完成逻辑电路的生成。SATA控制器(XC5VFX130T)的硬件实现平台选用XILINX公司的FPGA芯片XC5VFX130T-2FF1738,该芯片的相关信息参见。在XC5VFX130T中实现一个PLB2SATAIP模块的资源占用情况如表5-1所示。表5-1PLB2SATAIP在XC5VFX130T中实现的资源占用情况LogicresourcesUsedavailableutilizationBUFDSs11010%BUFGs83225%DCM_ADVs21216%GTX_DUALs11010%RAMB36_EXP82982%SliceRegisters2224819202%FlipFlops2223------------Latches1------------SliceLUTS2611819203%SliceLUT-FlipFloppairs3530819204%表5-1-2PLB2SATAIP在XC5VFX70T中实现的资源占用情况SliceLogicUtilization:NumberofSliceRegisters:2,902outof44,8006%NumberusedasFlipFlops:2,902NumberofSliceLUTs:3,097outof44,8006%Numberusedaslogic:2,815outof44,8006%NumberusingO6outputonly:2,475NumberusingO5outputonly:184NumberusingO5andO6:156NumberusedasMemory:251outof13,1201%NumberusedasShiftRegister:251NumberusingO6outputonly:250NumberusingO5andO6:1Numberusedasexclusiveroute-thru:31Numberofroute-thrus:219outof89,6001%NumberusingO6outputonly:215NumberusingO5outputonly:4从表5-1可以看出在XC5VFX130T-2FF1738中实现一个SATA控制器PLB2SATAIP只占用3%左右的Slice资源,所以在该片FPGA中就可以生成多达20个同样的SATA控制器(当产生多个SATA控制器时BUFDSs,BUFGs,DCM_ADVs资源是可以共用的),这么多的控制器可以并行工作实现阵列式存储。表5-2是国内外不同研究机构在不同芯片上实现SATA控制器的资源占用情况和接口形式。其中ASICS,Designgateway,HiTechGlobal三家公司是专业从事IP软核开发和销售的公司。从资源上来看,本人设计的SATA控制器与IP公司设计的SATA控制器是在同一个水平上的。本文设计的SATA控制器具有占用资源少、易升级、适应性广的优点。表5-2SATA控制器特性对比表芯片资源Slice接口形式开发单位XC5VFX130T-2652PLB+NPI本文XC5VFX70T-2725PLB+NPI本文XC5VLX50T-1579FIFOASICSXC5VLX50T-2861Wishboneslave+FIFODesigngatewayXC5VLX50T-21057Wishboneslave+FIFOHiTechGlobalXC4VFX60-101794XC4VFX603348AHB湖南大学图5-2所示这就是本文采用的“基于直接内存读写的存储架构”。存储数据时,从camlink接口/光纤接口/PCIE接口输入的数据通过MPMC的NPI接口直接写入高速缓存单元缓存,然后由多个SATA控制器以RAID0或RAID1或RAID0+1的方式将缓存的数据写入磁盘阵列;读取数据时,多个SATA控制器将磁盘阵列中的数据通过NPI接口直接写入高速缓存单元缓存,然后将高速缓存单元中缓存的数据按照存储数据时的顺序依次读出,并通过camlink接口/光纤接口/PCIE接口输出。图5-2存储系统框图为了更详细、清楚的描述高分辨率图像实时存储系统的工作原理和步骤,固将高分辨率图像实时存储系统中FPGA内的设计具体化,如图5-3所示。其中FPGA选用XILINX公司的XC5VFX130T-2FF1738,XC5VFX130T-2FF1738的结构和特性可以参见XILINX公司提供的技术手册。嵌入式处理器选用XC5VFX130T-2FF1738中内嵌的硬IP核PPC440,存储器控制器模块选用的是软IP核ppc440mc_ddr2,多端口存储器控制器组是由2个软IP核MPMC组成的,分别是MPMC_1和MPMC_2,SATA控制器组是由12个SATA控制器组成的,分别是SATA_ctrl1,SATA_ctrl2,SATA_ctrl3...SATA_ctrl12。此外,DDR2内存条1,DDR2内存条2和DDR2内存条3都是容量为512M字节、64位的DDR2内存条。磁盘阵列是由12块SEAGATES公司的硬盘组成(硬盘型号为ST3320418AS)。图5-3存储系统实例图实验结果与分析本文设计的SATA控制器是在XILINX公司的XC5VFX130T-2FF1738芯片上实现的,实验系统如图5-4所示,该实验平台是XILINX公司的ML510开发板(相关资料可以访问WWW.XILINX.COM网站)。图5-4高速存储实验系统照片实验1:不同帧大小持续顺序读写性能测试环境:FPGA中构建的存储架构如图5-3中所示,但是对某些模块进行了必要的增减。在图5-3中,嵌入式处理器选用XC5VFX130T-2FF1738中内嵌的硬IP核PPC440,软件代码存储在片上块RAM中,只选用了一个多端口存储器控制器MPMC_1、一个SATA控制器SATA_ctrl1和一个内存条DDR2内存条1。SATA_ctrl1控制一块硬盘,硬盘型号为ST3320418AS,接口传输率为3.0Gbps。本实验中,嵌入式PPC440设置完硬盘工作模式后,通过PLB总线将有规律的数据(写入有规律的数据主要是为了便于接收时测试数据正误)写入内存条1,对内存条进行初始化,SATA控制器就不断的、循环的读出这些数据作为向硬盘写数据的数据源。SATA控制器作为主设备向目标硬盘的LBA=1开始的扇区顺序写入数据,直到写完硬盘所有扇区,然后从LBA=1开始持续顺序的读回所有数据。持续读、写带宽等于总的读、写数据量除以总的读、写时间。总的时间是通过对固定频率的时钟计数换算得到的,总的数据量是通过对发送的数据帧计数换算得到的。图5-5和图5-6是数据帧长度为8K时持续顺序读写的性能图。图5-5不同硬盘持续顺序读性能图图5-6不同硬盘持续顺序写性能图图5-7SSD硬盘持续顺序读写性能图图5-7是使用两款SSD硬盘做的同样的实验。由图5-7可知,使用SSD硬盘SSDSA2SH064G1和SSDSA2SH032G1时,持续顺序读写带宽分别达到163MB/s和144MB/s。读写性能表现最好的传统机械硬盘ST3500418AS的持续顺序读写带宽分别为132MB/s和127MB/s。使用SSD硬盘比机械硬盘持续顺序读写带宽分别提高了23%和13%。目前,经过本人的优化后,该SATA控制器在XC5VFX70T上实现,对intel320系列SSD硬盘的持续顺序读写带宽分别为273MB/s和215MB/s.(硬盘型号:intelsolid-staledrive320series:300GB容量)该系列硬盘的文档见附件。我可以在xilinx公司的评估板ML507上将硬盘的读写现场演示。图5-8红线框是SSDSA2SH032G1硬盘网上公测性能指标(你可以自己上网站上查询)。该指标是网上公布的,是在PC机上使用ASIC芯片控制硬盘读写。从测试的数据可以看出,平均写入速度是155.3MB/s,平均读取速度是193.5MB/s.而使用FPGA实现的SATA控制器控制该硬盘读写其平均速度分别为142MB/s和162MB/s。通过比较两者的平均写入速度可以看出,本文设计的SATA控制器性能与PC机上的ASIC芯片的控制性能相当。图5-8SSDSA2SH032G1硬盘网上公测性能指标图',)

提供基于FPGA的SATA控制器介绍v1会员下载,编号:1700774456,格式为 docx,文件大小为9页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载