AMBA总线介绍,Amba总线

本作品内容为AMBA总线介绍,格式为 doc ,大小 93696 KB ,页数为 4页

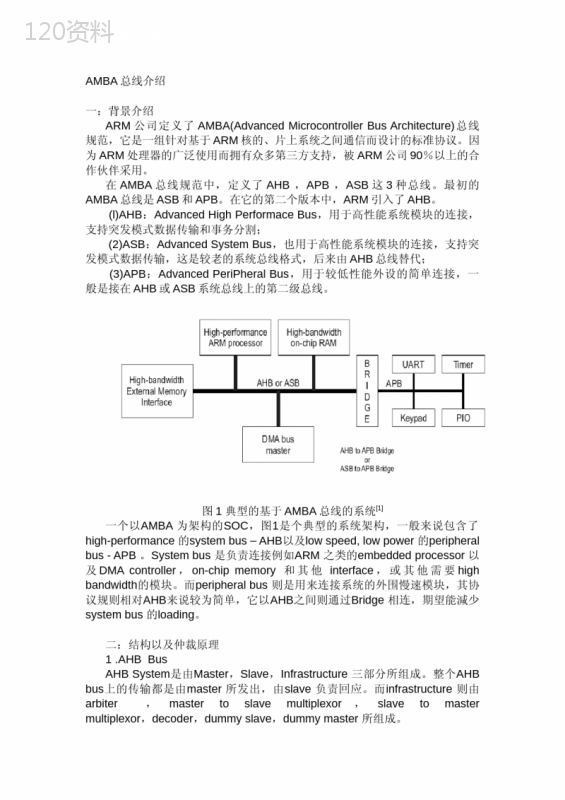

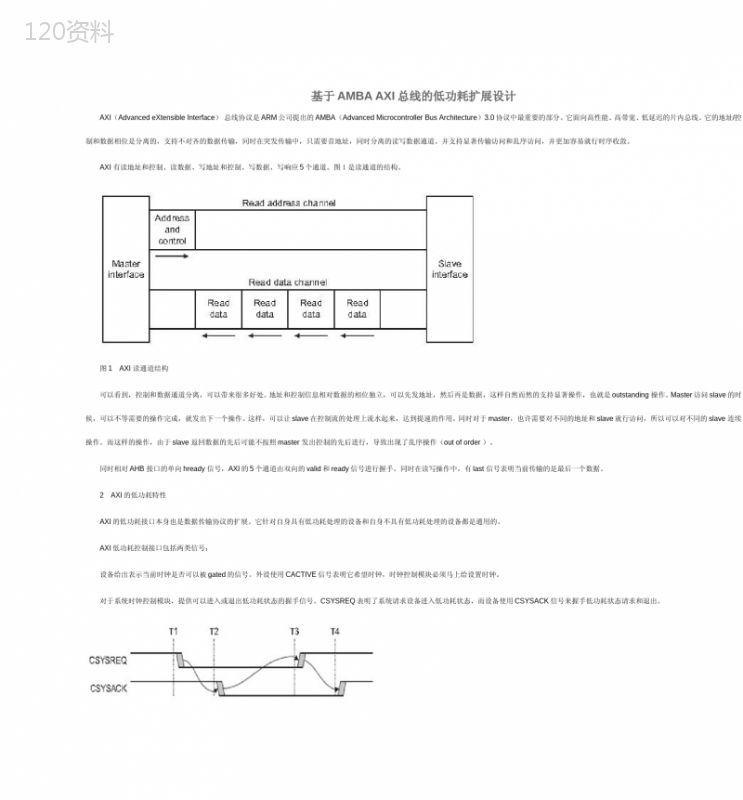

('AMBA总线介绍一:背景介绍ARM公司定义了AMBA(AdvancedMicrocontrollerBusArchitecture)总线规范,它是一组针对基于ARM核的、片上系统之间通信而设计的标准协议。因为ARM处理器的广泛使用而拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用。在AMBA总线规范中,定义了AHB,APB,ASB这3种总线。最初的AMBA总线是ASB和APB。在它的第二个版本中,ARM引入了AHB。(l)AHB:AdvancedHighPerformaceBus,用于高性能系统模块的连接,支持突发模式数据传输和事务分割;(2)ASB:AdvancedSystemBus,也用于高性能系统模块的连接,支持突发模式数据传输,这是较老的系统总线格式,后来由AHB总线替代;(3)APB:AdvancedPeriPheralBus,用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。图1典型的基于AMBA总线的系统[1]一个以AMBA为架构的SOC,图1是个典型的系统架构,一般来说包含了high-performance的systembus–AHB以及lowspeed,lowpower的peripheralbus-APB。Systembus是负责连接例如ARM之类的embeddedprocessor以及DMAcontroller,on-chipmemory和其他interface,或其他需要highbandwidth的模块。而peripheralbus则是用来连接系统的外围慢速模块,其协议规则相对AHB来说较为简单,它以AHB之间则通过Bridge相连,期望能減少systembus的loading。二:结构以及仲裁原理1.AHBBusAHBSystem是由Master,Slave,Infrastructure三部分所组成。整个AHBbus上的传输都是由master所发出,由slave负责回应。而infrastructure则由arbiter,mastertoslavemultiplexor,slavetomastermultiplexor,decoder,dummyslave,dummymaster所组成。AHB总线互联结构图【2】AHB支持多主设备,所以需要仲裁器。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layerAHB规范)。AHBArbitration的机制简述如下:当master想要accessbus时候,master将HBUSREQsignal(busrequest)给drivehigh(每个master都有自己的HBUSREQ信号),同一个时间可能有多个master都想要accessbus,因此arbiter在HCLK的risingedge去sample各个master的HBUSREQ信号后,需要决定哪个发出request的master有最高的priority(虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由设计工程师自行决定,AHB并没有规定priorityalgorithm,其中两个最常用的算法是固定优先级算法和循环制算法),然后将此master的HGRANT(busgrantsignal由arbiter给出)信号drivehigh,表示他可以accessbus了。(若原本已有master在accessbus,arbiter会把原本master的HGRANT信号给driveLOW,表示他已经丧失access的权利。当master正在进行fixed-lengthbursttransfer(固定长度的突发连续传输)时候,如果有更高priority的master发出了request,arbiter可以等待burst完成后再將busgrant给新的master,也可以在burst进行中就中断原来master的bus拥有权(ownership),让更高priority的master去accessbus。而被中断的master就需要重新发出request,等待下一次Grantbus时候继续完成burst了。若master想要进行的连续transfer是不可以中断的(比如在accesssharedmemory时候),则master可以在request时候,同时将HLOCK给drivehigh,告诉arbiter我要进行的是不可被中断的transfer,则当master获得accessbus权力后,arbiter将不会把busrelease给其它master,直到master自行将HLOCK给driveLOW,arbiter才会进行arbitration的动作【2】。2.APBBusAPB协议什么简单,APB主要是用在连接low-bandwidth外围设备上,例如UART等。它的bus架构不像AHB为Multi-Master,在APB里面唯一的的master就是APBBridge(与AHBBus相接),因此不需要arbiter以及request/grant信号。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。3APB桥APB桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。三;参考文献:1AMBA™Specification(Rev2.0)www.amba.com2IntrofuctiontoAMBABusSystem吴欣龙工程院/系统晶片技术中心工程师3http://blog.163.com/meteora_wzh/blog/static/369626752007102752315710/Or1200中的wishbone总线仲裁原理一:Wishbone信号线的说明Wishbone总线连接线可分为:同步信号线wb_clk_i;复位信号线:wb_rst_i地址线wb_addr_i[31:0];数据线:主IP核到从IP核的数据输出,输入线wb_dat_o[31:0],wb_dat_i[31:0I;控制线(常用)wb_cycwb_stb,wb_sel[3:0],wb_wewb_ack,wb_errwb_cyc:总线周期信号,有效代表一个主设备请求总线使用权或者正在占有使用权,当时不一定进行总线操作wb_stb:选通信号,有效代表主设备发起一次总线操作。wb_cyc是最高层的控制信号,只有wb_cyc这个信号有效wb_stb才有效wb_sel[3:0]:有效数据总线选择信号,标识当前操作数据总线上哪些位是有效的wb_we:写使能信号wb_ack,wb_err:主从设备间的操作结束方式信号,ack表示成功,err表示错误还有一些控制线比如tgd,tga,tgc等标签信号我们的系统没有用上(1)主设备发出的信号包括数据,地址信号以及控制信号wb_cycwb_stb,wb_sel[3:0],wb_we主设备接收的信号包括数据以及从设备反馈信号wb_ack,,wb_err(2)从设备与主设备正好相反从设备发出的信号有数据信号以及给主设备的反馈信号wb_ack,,wb_err从设备接收主设备发送过来的数据,地址信号以及控制信号wb_cycwb_stb,wb_sel[3:0],wb_we二:Wishbone的互联类型Wishbone总线提供了四种不同的IP核互连方式:(1)点到点(point-to-point),用于两IP核直接互连;(2)数据流(dataflow),用于多个串行IP核之间的数据并发传输;(3)共享总线(sharedbus),多个IP核共享一条总线;(4)交叉开关(crossbarswitch),同时连接多个主从部件,提高系统吞吐量。点对点连接是最简单的一种连接方式;数据流连接方式主要用于数字信号处理等应用场合;共享总线,它适用于系统中有两台或者多台主设备需要与一台或则多台从设备通信的场合,它只允许在任何一时刻最多只允许一对主设备和从设备通过共享总线进行通信。而交叉开关互联方式中,最多允许超过一对的主设备和从设备对同时惊醒通信,当然在任一时刻,一台从设备只能与一台主设备进行通信,两台主设备不能同时访问同一从设备。为了实现共享总线及十字交叉方式的互联,Wishbone总线用户必须自己实现仲裁(Arbitrator)逻辑模块。系统中采用的是共享总线和交叉开关互联2者兼有的连接方式,其总裁机制采用固定优先级,具体实现体现在源程序代码中。',)

提供AMBA总线介绍,Amba总线会员下载,编号:1700773872,格式为 docx,文件大小为4页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载