集成计数器功能描述及说明,十进制计数器的功能描述

本作品内容为集成计数器功能描述及说明,格式为 docx ,大小 114922 KB ,页数为 3页

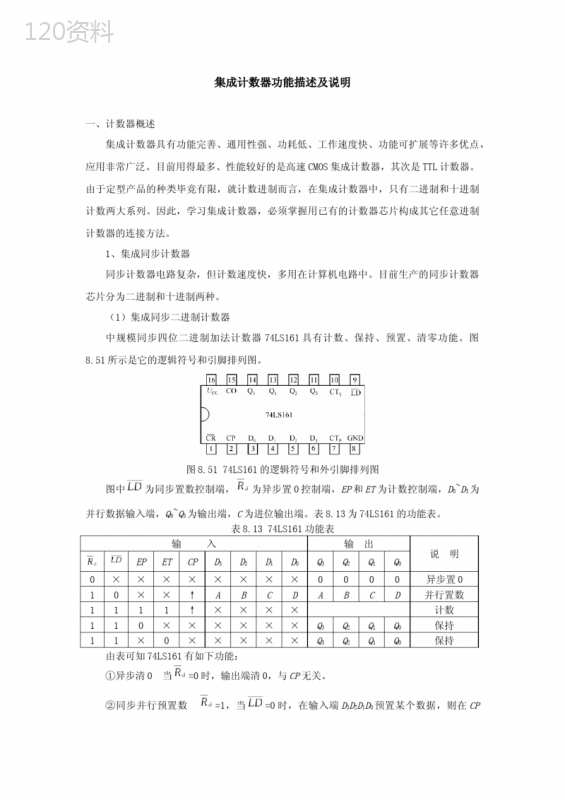

('集成计数器功能描述及说明一、计数器概述集成计数器具有功能完善、通用性强、功耗低、工作速度快、功能可扩展等许多优点,应用非常广泛。目前用得最多、性能较好的是高速CMOS集成计数器,其次是TTL计数器。由于定型产品的种类毕竟有限,就计数进制而言,在集成计数器中,只有二进制和十进制计数两大系列。因此,学习集成计数器,必须掌握用已有的计数器芯片构成其它任意进制计数器的连接方法。1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。目前生产的同步计数器芯片分为二进制和十进制两种。(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。图8.51所示是它的逻辑符号和引脚排列图。图8.5174LS161的逻辑符号和外引脚排列图图中为同步置数控制端,为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。表8.13为74LS161的功能表。表8.1374LS161功能表输入输出说明EPETCPD3D2D1D0Q3Q2Q1Q00××××××××0000异步置010××↑ABCDABCD并行置数1111↑××××计数110××××××Q3Q2Q1Q0保持11×0×××××Q3Q2Q1Q0保持由表可知74LS161有如下功能:①异步清0当=0时,输出端清0,与CP无关。②同步并行预置数=1,当=0时,在输入端D3D2D1D0预置某个数据,则在CP脉冲上升沿的作用下,就将输入端的数据置入计数器。③保持=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。在保持状态下,CP不起作用。④计数=1,=1,EP=ET=1时,电路为四位二进制加法计数器。当计到1111时,进位输出端C送出进位信号(高电平有效),即C=1。(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。它兼有二进制、五进制和十进制三种计数功能。当十进制计数时,又有8421BCD和5421BCD码选用功能,表8.14是它的功能表。图8.5274LS290的逻辑结构图表8.1474LS290的功能表输入输出R0(1)R0(2)S9(1)S9(2)QAQBQCQD110×000011×00000××111001×0×0计数0×0×0××0×00×外部接线Expressionisfaulty将QA接CP2,执行8421BCD码Expressionisfaulty将QD接CP1,执行5421BCD码由表可知,74LS290具有如下功能:①异步置0当R0(1)=R0(2)=1且S9(1)或S9(2)中任一端为0,则计数器清零,即QDQCQBQA=0000。②异步置9当S9(1)=S9(2)=1,则计数器置9,即QDQCQBQA=1001。③计数当R0(1)、R0(2)和S9(1)、S9(2)均至少有一个为低电平时,计数器处于计数工作状态。计数时有以下四种情况:若计数脉冲由CP1输入,从QA输出,则构成一位二进制计数器;若计数脉冲由CP2输入,从QDQCQB输出,则构成五进制计数器;若将QA接CP2,计数脉冲由CP1输入,输出为QDQCQBQA时,则构成8421BCD码十进制计数器;若将QD接CP1,计数脉冲由CP2输入,输出从高位到低位为QAQDQCQB时,则构成5421BCD码十进制计数器。在二、五、十进制的基础上,利用反馈控制置0或置9的方法,将QD、QC、QB、QA与R0(1)、R0(2)及S9(1)、S9(2)作适当连接,可得到二~十等九种进制的计数中的任一种。',)

提供集成计数器功能描述及说明,十进制计数器的功能描述会员下载,编号:1700753314,格式为 docx,文件大小为3页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载