十进制计数器设计,十进制计数器设计实验报告

本作品内容为十进制计数器设计,格式为 doc ,大小 659456 KB ,页数为 14页

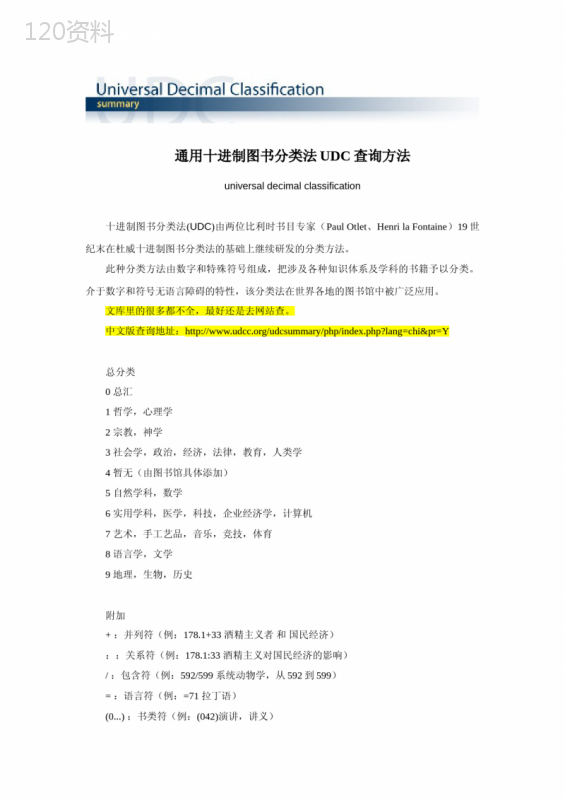

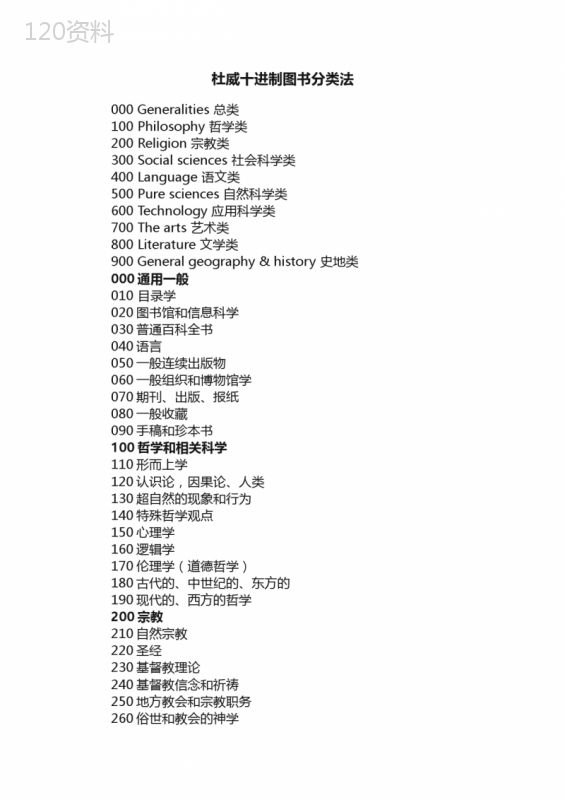

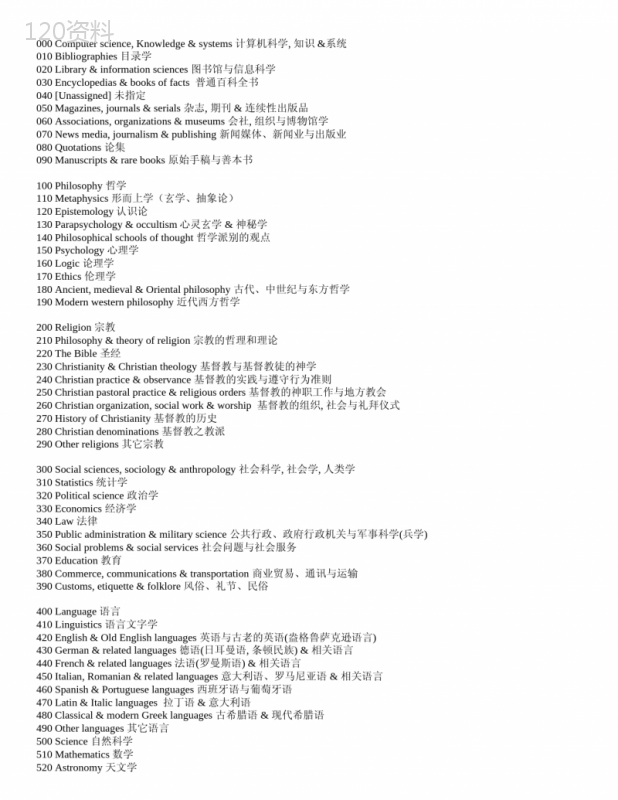

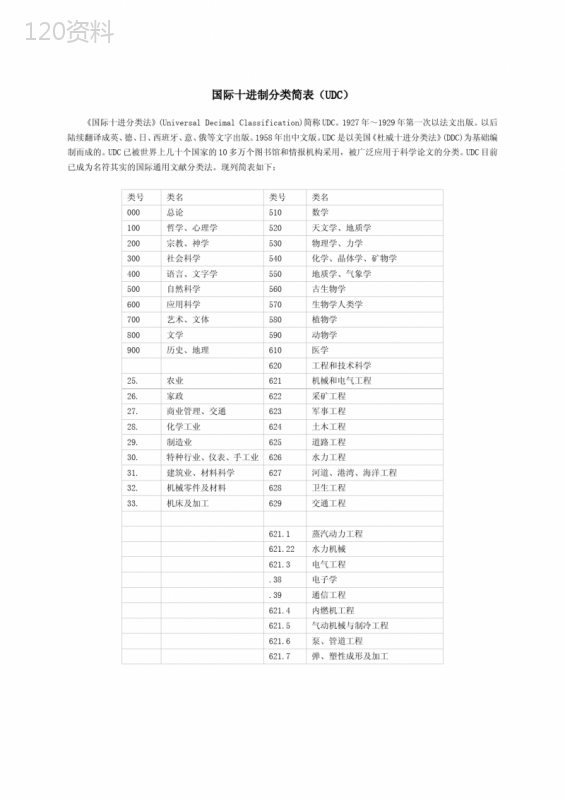

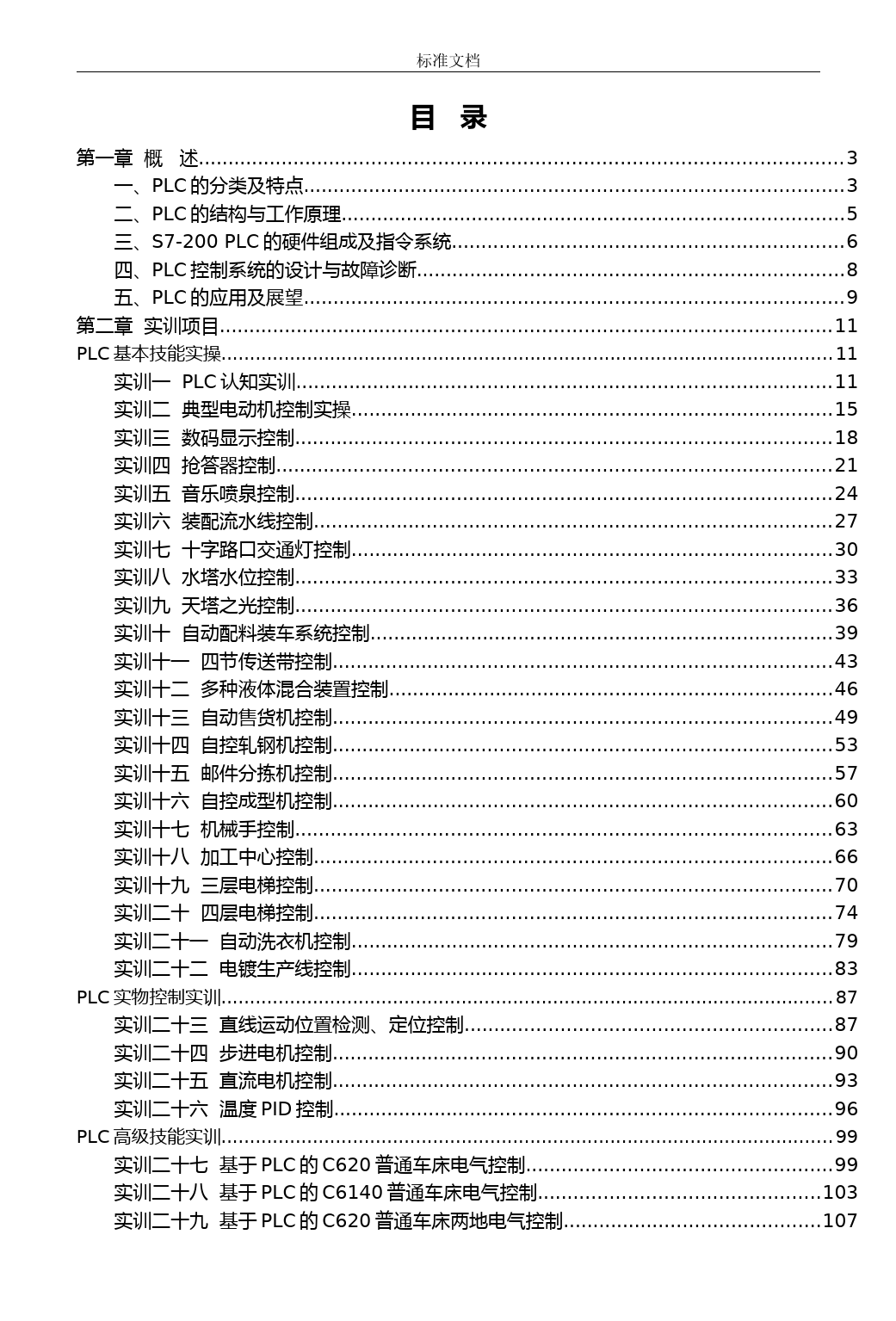

("十进制计数器设计-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN十进制计数器设计一、实验目的:熟悉QuartusII的Verilog文本设计流程全过程,学习十进制计数器的设计、仿真,掌握计数器的工作原理。二、实验原理:计数器属于时序电路的范畴,其应用十分普遍。该程序设计是要实现带有异步复位、同步计数使能和可预置型的十进制计数器。该计数器具有5个输入端口(CLK、RST、EN、LOAD、DATA)。CLK输入时钟信号;RST起异步复位作用,RST=0,复位;EN是时钟使能,EN=1,允许加载或计数;LOAD是数据加载控制,LOAD=0,向内部寄存器加载数据;DATA是4位并行加载的数据。有两个输出端口(DOUT和COUT)。DOUT的位宽为4,输出计数值,从0到9;COUT是输出进位标志,位宽为1,每当DOUT为9时输出一个高电平脉冲。RST在任意时刻有效时,如CLK非上升沿时,计数也能即刻清0;当EN=1,且在时钟CLK的上升沿时刻LOAD=0,4位输入数据DATA被加载,但如果此时时钟没有上升沿,尽管出现了加载信号LOAD=0,依然未出现加载情况;当EN=1,RST=1,LOAD=1时,计数正常进行,在计数数据等于9时进行输出高电平。三、实验任务:在QuartusII上将设计好的程序进行编辑、编译、综合、适配、仿真,从时序仿真图中学习计数器工作原理,了解计数器的运行情况及时钟输入至计数器数据输出的延时情况。四、实验步骤:(一)、建立工作库文件和编辑设计文件任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为WorkLibrary(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。(1)新建文件夹:在盘建立并保存工程,将文件夹取名Jishuqi。(2)输入源程序:打开QuartusII,选择菜单File\uf0e0New\uf0e0DesignFiles\uf0e0VerilogHDLFile\uf0e0OK(如图1所示)。图1在空白处工作框处输入任务要求中的代码,代码如下:moduleCNT10(CLK,RST,EN,LOAD,COUT,DOUT,DATA);inputCLK,EN,RST,LOAD;input[3:0]DATA;output[3:0]DOUT;outputCOUT;reg[3:0]Q1;regCOUT;assignDOUT=Q1;always@(posedgeCLKornegedgeRST)beginif(!RST)Q1<=0;elseif(EN)beginif(!LOAD)Q1<=DATA;elseif(Q1<9)Q1<=Q1+1;elseQ1<=4'b0000;endendalways@(Q1)if(Q1==4'h9)COUT=1'b1;elseCOUT=1'b0;endmodule(3)保存文件:选择File\uf0e0Saveas,选择保存路径,即刚才新建文件夹Jishuqi,文件名应与实体名保持一致,即CNT10,点击保存后会跳出“Doyouwanttocreateanewprojectwiththisfile”选择“是”,则进入如下界面,如图2所示。图2点击Next,进入“工程设置”对话框,第一行表示工程所在的文件夹,第二行为工程名,可以与顶层文件的实体名保持一致,也可以另取别的名字,第三行为当前工程顶层文件的实体名,如图3所示。图3点击Next,进入ADDFILE对话框,单击AddAll按钮,将工程相关的所有Verilog文件加进工程,也可以单击“Add...”选择性加入,从工程目录中选出相关的Verilog文件,然后点击Next,当先直接建立工程时,需要自己添加,如图4所示。图4(4)选择目标芯片:我们选用的是CycloneIII系列的EP3C55F484C8,在Family栏选择芯片系列——CycloneIII,在窗口右边的三个下拉列表框选择过滤条件,分别选择Package为FBGA、Pincount为484和Speedgrade为8,点击Next,如图5所示。图5(5)工具设置:进入EDA工具设置窗口,有三个选项,分别是选择输入的HDL类型和综合工具、选择仿真工具、选择时序分析工具,这是除QuartusII自含的所有设计工具以外的外加的工具,如果不作选择的,表示仅选择QuartusII自含的所有设计工具,本次不需要其他的设计工具,可以直接点击Next,如图6所示。图6(6)结束设置:进入“工程设置统计”窗口,列出了与此工程相关的设置情况,设置完成,点击Finish,如图7所示。图7(二)、编译配置好后就可以进行编译了,点击Processing\uf0e0StartCompilation命令,启动全程编译编译成功后的界面如图8所示。图8(三)、时序仿真(1)打开波形编辑器:File\uf0e0New\uf0e0Verification/DebuggingFiles\uf0e0VectorWaveform\uf0e0OK,即出现空白的波形编辑器,如图9所示。图9(2)设置仿真时间区域:Edit-->EndTime在Time栏中输入50,单位选择“us”,点击确定并保存波形文件,如图10所示。图10(3)点击Edit\uf0e0Insert\uf0e0InsertNodeorBus\uf0e0NodeFinder\uf0e0List\uf0e0>>\uf0e0OK,如图11所示。图11(4)编辑输入波形:首先进行时钟窗口设置:点击左边的输入CLK的周期为,50%的占空比,如图12所示,设置EN、RST与LOAD,将它们设置为高电平。图12接着进行总线数据格式设置和参数设置:点击输入数据信号DATA的左边的+号,能展开此总线中的所有信号;如果双击此+号左边的信号标记,将弹出对该信号数据格式设置的NodeProperties对话框,在该对话框的Radix下拉列表中有四种选择,这里选择十进制表达方式。其次输入波形数据:由于DATA是4位待加载的输入数据,需要设置输入数据。用鼠标在所示信号名DATA的某一数据区拖拉出来一块蓝色区域,然后单击左侧工具栏的按钮,在弹出窗口输入数据如1,继而在不同区域设置不同数据。这里为方便观察,输入的数据依次是1,5,7,9,4,如图13所示。图13(5)仿真仿真器参数仿真:选择Assignment\uf0e0Settings命令,在Settings窗口下选择Category\uf0e0SimulatorSettings。在右侧的Simulationmode下拉列表中选择Timing,即选择时序仿真,并选择仿真激励文件名。选择SimulationPeriod栏,确认选中了“Runsimulationuntilallvectorstimuliareused”,如图14所示。图14启动仿真器:Processing\uf0e0StartSimulation,直至出现Simulationwassuccessful,仿真结束,然后会自动弹出“SimulationReport”,点击输出信号“DOUT”旁边的“+”,展开总线中的所有信号,可以便于我们观察和分析波形,如图15所示。图15(四)应用RTL电路图观察器Tools\uf0e0NetlistViewers\uf0e0RTLViewer,结果如图16所示。图16五、实验心得通过几周的学习,我了解了FPGA编程语言的使用方法,通过设计实验项目,我掌握了QuartusII软件的用法以及十进制计数器的工作原理。在这个过程中,让我明白了动手能力的重要性,同时也使我认识到自己所学的知识还很欠缺,要加强这方面的学习。",)

提供十进制计数器设计,十进制计数器设计实验报告会员下载,编号:1700830246,格式为 docx,文件大小为14页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载