AMBA-APB4-与-AMBA3-AHB-Lite-1.0-协议介绍

本作品内容为AMBA-APB4-与-AMBA3-AHB-Lite-1.0-协议介绍,格式为 docx ,大小 126403 KB ,页数为 8页

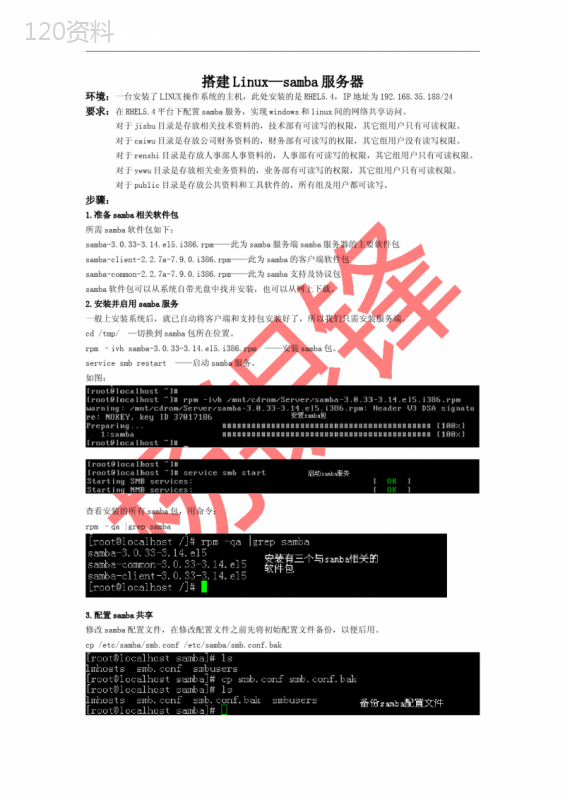

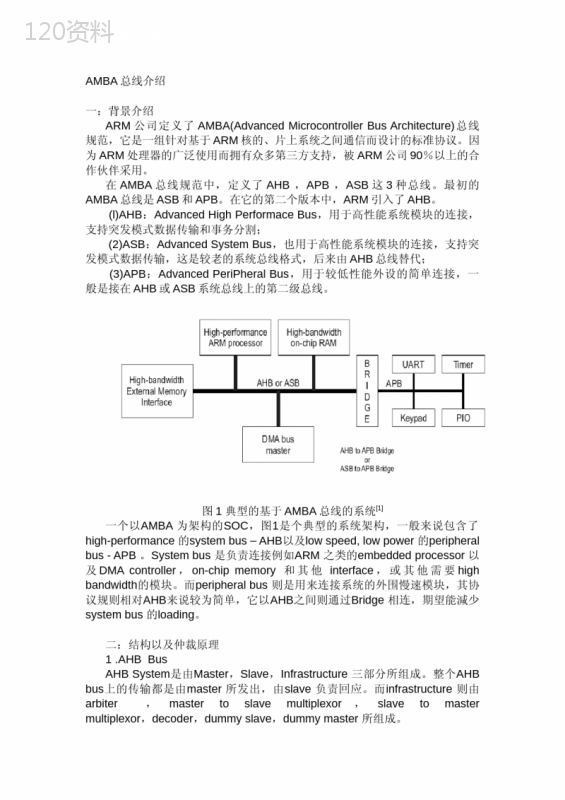

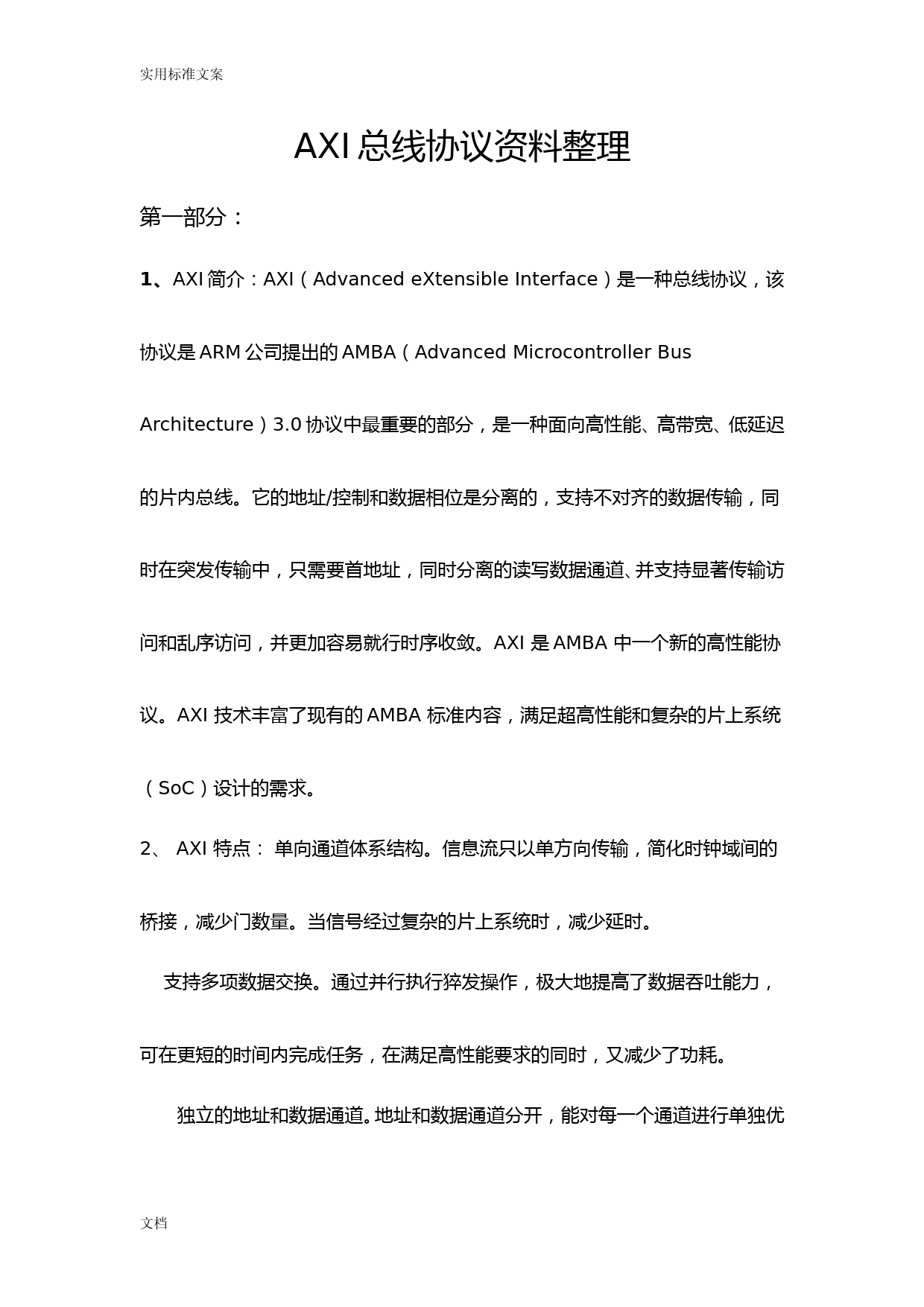

('AMBAAPB4与AMBA3AHB-Lite1.0协议介绍2013年09月18日16:09绝对好文关键词:AMBA,APB4,AHB-Lite作者:AllenZhan[介绍]根据ARM的说法,今天AMBA已经成为了业界事实上的总线标准.本文我们简单对AMBA4中的APBv2.0(也称为APB4),以及AMBA3AHB-Litev1.0进行简单的了解.我们的介绍集中在,我们比较有兴趣的地方.尽管如此,也可能几乎覆盖了协议中几个最重要的部分.[AMBAAPB]AMBAAdvancedMicrocontrollerBusArchitecture,由ARM定义的总线架构(标准),由一个协议家族组成.ARM声称这一标准已经称为事实上的uController业界通用标准.APBTheAdvancedPeripheralBus(APB)是AMBA协议家族中一个组成部分.它被定义为一个low-cost的接口,为了最小能耗与减小接口的复杂性进行的优化设计.被用于连接通用外围,比如timers,inerruptcontrollers,UART是,andIOs.通过system-to-peripheralbusbridge与mainsystembus相连,有助于降低能耗.APB版本当前(2013年9月),最近的APB协议版本是AMBAAPBProtocolSpecificationv2.0.或者因为属于AMBA4家族中的发布协议,一般也被称为APB4.而在第一个版本(APB2)中,APB的基本组元,APBbridge与APBslave被定义.而在APB3中,Readysignal被引入,这意味着增加了操作状态中,增加了waitstate.另外增加了PSLVERR,用于错误报告的signal.最近的APB4,增加了PPROT与PSTRBsignal.APBbridge与APBslave我们可以挂载各种"慢速"的外设在APB上,比如IO,比如UART,比如SPI,etc.它们都作为slave的角色存在.但是,我们想想看,bridge这个role就蛮有意思.它实际上暗示我们,APB不能"单独存在".我们这里所谓不能"单独存在"的意思,是说APB一定不能直接连接在processor上(或者说armcore上).而最可能的,是通过APBbridge而连接在高速的bus上.实际上,在AHB-Lite协议中,我们发现APBbridge被作为AHB-Lite的slave而被定义.DatabusesAPB协议有两个独立的databus,一个用来读data,一个用来写data.因为没有独立的握手信号,所以在两根bus上,同一时刻数据传输不能同时发生.WriteTransfers我们简单对APB的trasfers过程进行分析,比如我们分析writetransferwithnowaitstates:[图例1:Writetransferwithnowaitstates]T0:IdlestateT1:SetupstatewriteaddressPADDR,writedataPWDATAsetupstate仅仅只保持1pcsclockcycle,而在下一个PCLK的上升沿,一定进入Accessstate.T2:AccessstateAPBbridge通过拉高PENABLE,通知slave第二阶段(也就是accessphase)开始.因为是nowaitstates,我们见到了PREADY在此被拉高,表示slave通知bridge,在下一个PCLK的上升沿,本次transfer的过程可以结束.T3:finishtransfer,thenenterIdlestateagainorthenextsetup.PREADY拉低,说明slave通知本次transfer结束.在PREADYunasserted之前,PADDR,PWDATA,以及其他的signals都应该保持有效.从上述时序中,我们了解到,writetransfer看来至少需要3cycles.setup-access-finish而在一个writetransferwithwaitstates时序中,[图例2:Writetransferwithwaitstates]我们见到了,Slave通过unassert的方式(拉低),延迟了2pcscycles(根据图例的例子),这样在T2状态上的拉高动作,被延时到T4进行拉高.也就是Slave通知在T5cycle中结束本次transfer.这就是通过PREADY引入了waitstate后现象,我们注意到,一般的术语被称为"extendthetransfer".OperatingStatesReadTransfer的情形与WriteTransfer类似,这样,我们就基本完备讲述了APBprotocol,附上OperatingStates进行理解:[图例3:StateDiagram]transfercyclesAPBprotocol中,明确指出:"每个Transfer至少消耗2cycles".而我们检查,即使是transferwithnowaitstate,也最少消耗了3cycles.这里我们理解,在图例1中,T3状态下,finish本次transfer后,如果要连续操作下一个写传递的过程,那么则在T3状态下保持PSELasserted,配合PREADYunasserted,恰好又进入了如T1cycle相同的setupstate,这时需要bridge更新地址PWRITE,以及数据PWDATA.也就是在连续transfer(针对同一个slave)的操作中,transfer最少只消耗2cycle.我们没有在APB协议中,获得上述猜测的详解,我们保留上述对"2cycles"的理解猜测于此.总结我们通过对APBprotocol的理解,得知APB是unpipeline的bus.无论如何,setupstate将占据一个cycle,而accessstate将占据另一个.这种unpipeline的设计,很可能就是APB被作为连接外围的,而不是用于processor之间的memory连接的BUS的重要原因.因其不要求外围在一个cycle中对address进行取样,这也给外围更多的时间反应,至少比较而言,使用APB的外围可以具备更小的bandwidth.[AMBAAHB-Lite]AHB-LiteAHB:AdvancedHigh-performanceBus用于高表现力高clock频率的系统.最经常的使用是连接internalmemeorydevice,externalmemoryinterface,以及highbandwidth外围.其基本组元是:Master,Slave,Decoder,Multiplexor.在address/controlphase与dataphase中,存在fixedpipeline.AHB:仅仅支持AMBAAXIprotocol的功能子集(subset).AHB-Lite:如果除去在master与slaveIP开发中不需要的部分,则AHBprotocol的这个subset则定义为AHB-Lite.Operation每一个trasfer都包括Addressphase与DataPhase.Address不允许被extend,即便是来自Slave的请求,因此我们可以想象,全部的Slaves都必须在Addressphase(1cycle)完成samplingaddress.但是与APB一样,Slave也可以通过HREADYsignal请求extenddataphase,增加额外的时间去sampledata.HRESPsignal被用来说明transfer的成功与否.Address总是可以在一个singleHCLKcycle中完成,除非是之前的bustransfer被extend(我们理解,这里应该是只有data才能做这个extend).Data可以占有数个HCLKcycle,这取决于HREADYsignal是否extendtransfer.因此,Addressphase可以与Dataphase的overlapping,就是pipeline的基础.[图例4:在不同地址上的3个transfer的例子]TransfertypesTransfertypes包括:IDLE,BUSY,NONSEQ,SEQ同猜想的一样,对于Slave,可以通过HREADY实现extendtransfer,我们觉得,这或者就是"较为慢速"的Slave实现delay的方式.而Master如果在HTRANS[1:0]中使用BUSY,也可以在bursttransfer的过程中,插入idlecycles.这让人觉得,这应算是master试图做delay的方式.[图例5:BUSYTransfertype]值得注意的是,该例子,使用了4-beat的burstoperation.Lockedtransfers通过HMASTLOCK,master可以要求完成"锁定"的transfer,不能被打断.而这个用法,往往在多个master的用法中存在.[图例6:Lockedtransfers]Defaultslave如果不存在的的memorymap被master点中,AHB-Lite协议给出了一个解决方案,就是必须存在一个增加的defaultslave来进行回应.SlavetransferresponsesAHB-Lite协议中指出,Master一旦开始一个transfer后,将无法主动取消这个transfer.因此,通过来自Slave的HRESPsignal的状态,判断transfer的成功与否将是重要的.HWDATA与HRDATA同APB协议一样,databus的read与write是分离的.所以不需要"三态"的drivers.我们此时有点大脑短路,不太理解这里的意思,这应该是说,如果我们在单一的,而不是分离的databus上实现readdata以及writedata,那么我们就需要"三态驱动器"?这里的tristate为何意?--有知道的同行,这里定能有教于我.[参考文献]1.AMBA3AHB-LiteProtocolv1.0Specification2.AMBAAPBprotocolv2.0Specification[结语]让我们引用Sailing的文章"ARM与x86之4--EAGLEisComing!"(From:http://blog.sina.com.cn/s/blog_6472c4cc0100mnza.html)中的论述AMBA的片段作为结语:<剪切>"最令Intel尴尬的是,x86处理器并没有一个与AMBA总线类似的SoC平台总线,这是Intel进军嵌入式领域一个不小的障碍。Intel或者定义一条全新的SoC平台总线,或者集成AMBA总线。从加速推出产品的角度上,直接使用AMBA总线无疑是一条捷径。而世上没有捷径,从更长远的时间上看,借用AMBA总线,会使ARM阵营更加强大。最初的所谓捷径不过是为他人做的嫁衣裳。""面对ARM内核,Intel并不畏惧,面对AMBA总线阵营,Intel只剩下无奈。可以预计在相当长的一段时间里,Intel无法推出一条能和AMBA总线抗衡的SoC平台总线。Intel只能暂时向AMBA总线示弱。"<剪切>',)

提供AMBA-APB4-与-AMBA3-AHB-Lite-1.0-协议介绍会员下载,编号:1700635577,格式为 docx,文件大小为8页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载