一种兼容SMBus协议的I2C总线控制器的设计

本作品内容为一种兼容SMBus协议的I2C总线控制器的设计,格式为 docx ,大小 45740 KB ,页数为 10页

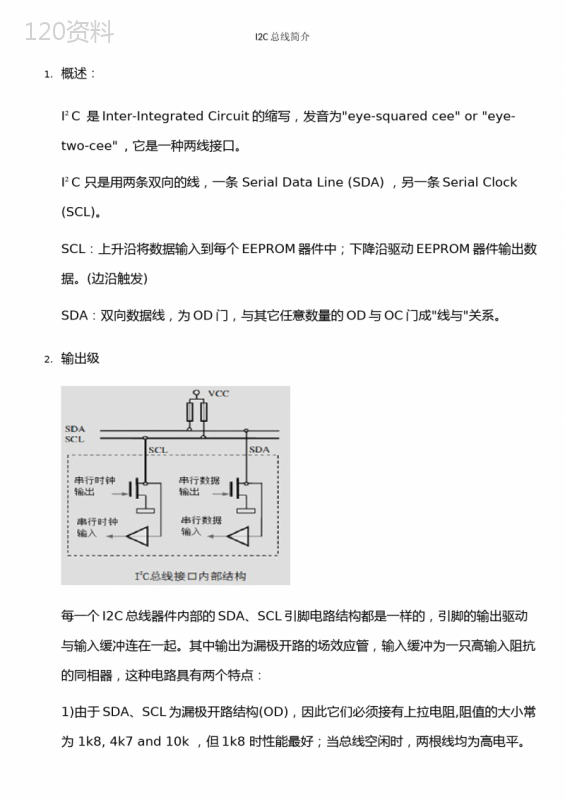

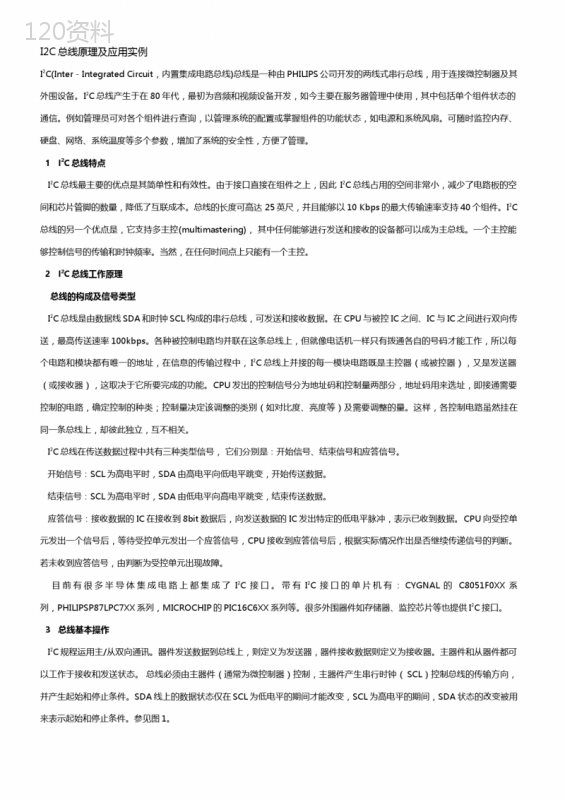

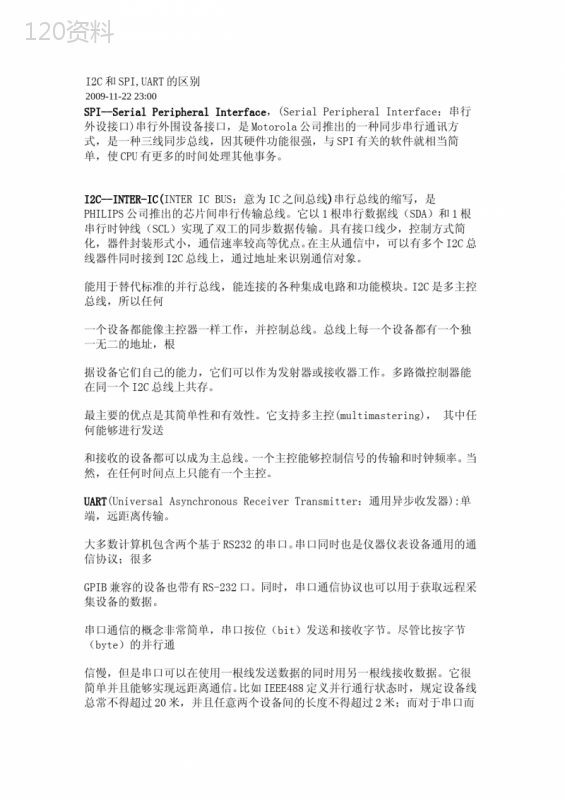

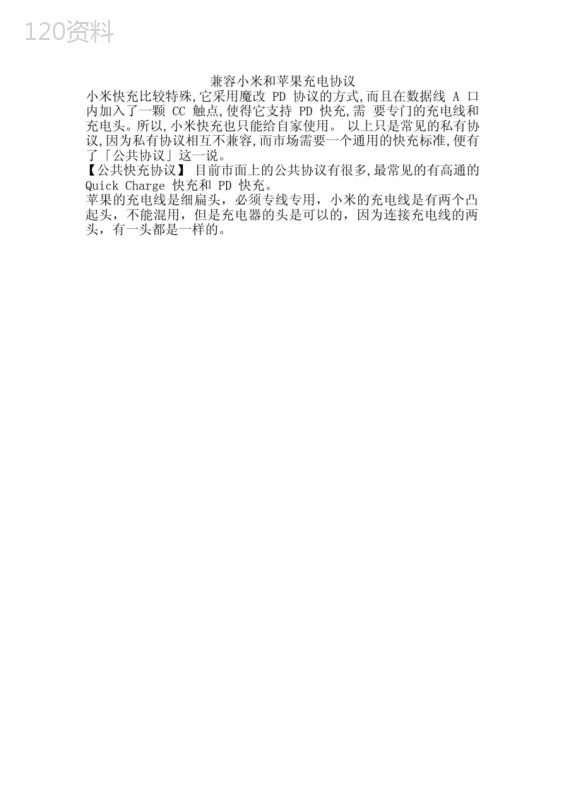

('一种兼容SMBus协议的I2C总线控制器的设计王芬芬;冯海英;丁柯【摘要】为了满足片上系统(SOC,SystemOnChip)中高性能且低成本的知识产权(IP,IntelligenceProperty)复用技术,提出了一种兼容SMBus2.0(SMBus,SystemManagementBus)协议的I2C(I2C,Inter-integratedcircuit)总线控制器的设计.该设计既保证I2C和SMBus各自的功能和时序,又极大地节省了硬件资源,可广泛应用于这两者的外设通信环境中.此外,该设计基于高性能外设总线(APB,AdvancePeripheralBus)接口,采用VerilogHDL实现,可方便地集成到SOC系统中.最后,搭建仿真验证平台,验证了该I2C总线控制器的兼容性,证明其总线功能的完善性、总线时序的规范性以及总线通信的稳定性.【期刊名称】《电子与封装》【年(卷),期】2018(018)009【总页数】7页(P20-25,32)【关键词】I2C总线;SMBus总线;SOC;VerilogHDL【作者】王芬芬;冯海英;丁柯【作者单位】中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072【正文语种】中文【中图分类】TN4021引言I2C总线[1]是Philips公司开发的一种简单、双向二线制同步串行总线[1]。通过串行时钟线SCL和串行数据线SDA即可在连接于总线上的器件之间传送信息,因而广泛应用于微控制器、EEPROM、A/D转换器及电子通信领域[2]。SMBus2.0协议是在I2C协议基础上研发出来的系统管理总线协议[3],它基于I2C操作原理,继承了I2C总线的特点和优点,起初是为智能电池、充电电池和与其他系统通信的微控制器之间的通信链路而定义的,后来也被用来连接各种设备,包括电源相关设备、系统传感器、EEPROM通信设备等,目前已成为在智能电池及低速率管理设备上被广泛采用的协议标准[4]。实现I2C总线协议时主要有两种方法:第一种是利用SOC芯片的两个引脚去模拟SDA和SCL,并利用软件模拟控制器的接口功能,这种方法通用可行但移植性差,占用资源多,软件规模大,不易于维护;第二种方法是利用I2C总线控制器IP,在SOC芯片中嵌入I2C总线接口,利用硬件设计I2C总线控制器,然后集成到SOC系统中,这种方法移植性好,但要求I2C总线控制器功能完善且占用较低的硬件资源。王炳文等[5]基于可编程逻辑设计了一种I2C总线主机控制器,通过FPGA状态机的组合扩展出I2C总线,相比完全用软件模拟I2C时序的方法减小了软件的工作量,但扩展出的I2C总线仅支持部分传输方式。张文梅等[6]设计了一种功能可扩展的I2C控制器,但该控制器只能作为从机控制器,且只能进行写操作,不可进行读操作。宋杰等[7]的设计中采用了异步先进先出来同步APB总线和I2C总线之间的数据交换,且设计满足通信的100kHz和400kHz两种数据传输速率要求,但不支持从机的10位地址模式,也不支持主机的时钟同步和总线仲裁功能。胡春媚等[8]设计了一种I2C主从控制器,实现了I2C总线协议规范的基本功能。陈涛[9]设计了一种SMBus接口的控制器用于智能电池系统,实现了SMBus总线协议规范的基本功能。在芯片管脚资源受限的系统中,单独设计一种既能覆盖I2C总线也能覆盖SMBus总线的控制器具有重要的意义。本文设计了一种兼容SMBus2.0协议的I2C总线控制器,既保证各自的功能和协议规范,又极大地节省了硬件资源。该控制器连接串行I2C/SMBus总线,可配置为主机或从机模式,且有多主机功能;而且该控制器由状态机控制,同时满足I2C/SMBus的通信模式和通信时序。此外,本文基于APB总线设计,采用VerilogHDL语言实现,使得该控制器很容易集成到基于AMBA总线的SOC系统,从而得到更广泛的应用。本文首先简要介绍了I2C总线的基本原理,分析了I2C总线和SMBus总线的相同点和不同点;然后对整个I2C总线控制器进行了层次分明的模块化设计,并深入阐述了各个模块的功能及I2C和SMBus兼容性的实现;最后,通过仿真验证了该I2C总线控制器的兼容性。2I2C总线与SMBUS总线比较I2C串行总线包含2根信号线:串行数据线SDA和串行时钟线SCL,这2根线都是双向的,并通过一个电流源或上拉电阻连接到正的电源电压[1]。当总线空闲时,这两根线均处于高电平状态。此外,连接到总线的器件输出级必须是漏极开路或集电极开路,这样就可将多个I2C设备的串行数据线SDA和串行时钟线SCL分别进行线与的功能,同时连接到一个通信网络中。该总线结构图如图1所示。每个连接到I2C总线的设备都有一个唯一的设备地址,而且都可作为一个主机或从机用于发送或接收数据。图1I2C总线结构图在I2C总线上,执行数据传输时主机和从机的关系不是恒定的。主机用于启动总线传输数据,产生START起始条件和STOP结束条件,发送设备地址并产生时钟信号,此时任何被寻址的器件均被认为是从机。而此时数据传送的方向决定了I2C器件是发送器还是接收器,I2C总线的数据传输时序如图2所示。图2I2C总线协议SMBus系统管理总线也是一种同步串行总线,包括数据线SMBDAT(本文记做SDA)、时钟线SMBCLK(本文记做SCL),还有一个可选信号为SMBALERT。它基于I2C总线协议规范,与I2C的数据有效性是一致的,数据传输格式也相同;但二者之间存在很多差异,在规范[10]中的多个协议层都有详细说明,本文从二者设计兼容的角度将必须考虑和实现的差异总结为3个方面:(1)SMBus与I2C在时序方面有较多差异,见表1,要做到I2C与SMBus设计兼容,必须正确地把二者的时序可靠地组合起来使用,使得二者都要满足各自的协议规范。表1SMBus与I2C时序的不同点时序不同点SMBusI2C通信快速模式不支持时钟频率高达400kHz数据保持时间300ns0时钟低电平超时时间tTIMEOUT25~35ms无定义从机的时钟低电平扩展累计时间tLOW:SEXT0~25ms无定义主机的时钟低电平扩展累计时间tLOW:MEXT0~10ms无定义(2)SMBus为了提高数据传输的可靠性,增加数据包错误校验(PacketErrorChecking,PEC)功能,主要用来检测或校验数据传输中出现的错误,I2C未作类似说明。(3)SMBus设备地址类型可划分为很多种,如保留地址、目的性分配地址、动态分配地址等。这些地址的划分运用于不同协议层的特定场合或特定目的。3I2C总线控制器设计本文设计的片上I2C总线控制器基于APB总线设计,且兼容SMBus总线协议。APB总线是由ARM公司开发的一种简单SOC总线,它由一个APBBridge和多个APBSlave组成,主要用来连接一些低速外围设备,因此该I2C总线控制器兼容性强,可以方便地集成到任何基于APB总线的SOC系统。3.1设计框架该I2C总线控制器支持主机或从机模式,能够控制所有I2C和SMBus总线特定的时序、协议、仲裁,支持7位和10位地址模式,支持通信速率标准模式高达100kHz和快速模式高达400kHz,同时满足SMBus的超时检测功能和PEC检测功能。I2C总线控制器设计结构图如图3所示,包括4个子模块:APB总线接口模块、SDA控制单元、SCL控制单元和状态机控制单元。图3I2C总线控制器结构图3.2APB总线接口设计APB总线接口模块是整个I2C总线控制器接口的控制部分,使I2C总线控制器的硬件行为与APB总线协调一致,负责实现与片上APB总线的互联及数据交换,所以设计了基于APB总线的接口寄存器,该寄存器的功能描述见表2。MCU可通过APB总线对I2C总线控制器的寄存器进行配置、数据读写和中断处理等操作,从而控制I2C总线控制器的工作模式及工作流程,实现I2C总线的数据通信。表2寄存器描述寄存器名称描述CR控制寄存器:主要配置工作模式、通信格式、通信时序等;AR地址寄存器:主要配置7位或10位设备地址及读写位R/W;DR数据寄存器:用来存储发送或接收的数据;SR状态寄存器:用来存储发送、接收等状态标志及校验、超时等传输错误状态标志;PECRPEC寄存器:用来存储计算的PEC字节;CCR时钟控制寄存器:主要配置通信模式及速率;TIMEOUTR超时控制寄存器:主要配置超时时间。3.3SCL控制单元设计SCL控制单元是对I2C总线控制器SCL总线的控制,主要作用是通过主机时钟产生、从机时钟拉伸和SMBus超时检测子模块结合时钟控制逻辑,产生SCL总线的时序,使其既满足I2C的SCL总线时序,又满足SMBus的SCL总线时序。3.3.1主机时钟产生当该控制器配置为I2C主机,配置CCR的通信模式,确定为I2C的标准模式、快速模式或SMBus模式;配置CCR的时钟分频系数,产生特定的SCL时钟频率;其中I2C的标准模式和SMBus模式的SCL占空比采用1∶1,CCR的时钟分频系数配置见公式(1),I2C快速模式的SCL占空比采用2∶1,CCR的时钟分频系数配置见公式(2),式中fPCLK表示主时钟PCLK的时钟频率,fSCL表示I2C/SMBus的总线通信速度;在时钟分频时必须实施时钟同步机制,以支持多主机环境和从机时钟拉伸。为了时钟同步,从SCL下降沿开始计数时钟低电平的个数,一旦计数到CCR的时钟分频系数,就释放SCL到高电平;从SCL上升沿开始计数时钟高电平的个数,一旦计数到CCR的时钟分频系数,就将SCL拉低到低电平。为保证兼容性,还必须同时保证I2C时序和SMBus时序的正确性,为了满足数据保持时间和建立时间以及时钟上升时间和下降时间,从SCL下降沿开始计数数据保持时间的个数,然后再计数数据建立时间的个数。考虑到硬件设计简单化且减少硬件面积,设计时充分结合I2C和SMBus两者时序的共同点和差异,将数据建立时间和保持时间根据主时钟进行了分类和归纳,见表3,对比I2C规范协议中的时序参数说明及SMBus2.0规范协议中的时序参数说明,表3的时序设计可同时满足I2C和SMBus的时序要求。表3I2C/SMBus时序参数主时钟PCLK/MHzsetup(硬件设计PCLK个数)hold(硬件设计PCLK个数)tSU:STA/μstHD:STA/μs2~5631.2~3.00.6~1.56~101261.2~2.00.6~1.011~202491.2~2.180.45~0.8121~3036121.2~1.710.4~0.5731~3648151.33~1.550.42~0.483.3.2时钟拉伸在总线传输期间,主机或从机可以选择在字节传输之间拉伸时钟低电平周期,用以处理已接收的数据或准备发送的数据或执行实时任务,在这种情况下,I2C和SMBus总线控制器就需要支持时钟拉伸功能。3.3.3SMBus超时检测主机或从机根据需要可以实时拉伸时钟总线,但SMBus2.0总线规范对在总线传输期间的时钟拉伸的累积值有严格限制,而I2C没有这个限制。当配置为SMBus设备时,设计了3种超时检测:第一种,时钟低电平超时检测,不论是主机或从机,一旦检测到SCL下降沿就开始计数,35ms内出现SCL上升沿,则计数器清零;一旦超过设置的超时阈值,见公式(3),那么所有的控制寄存器和状态寄存器及状态机都进行复位操作,同时主机在SCL和SDA总线上产生STOP条件,从机释放SCL和SDA总线为高电平;第二种,对从机的时钟低电平扩展累计时间tLOW:SEXT进行检测,在25ms内总线从START开始的一次传输期间,一旦检测到从机在字节传输之间或一个字节传输完毕后拉伸时钟低电平,就开始计数,该计数器一直累计,一旦超过设置的超时阈值,见公式(4),或检测到STOP条件,则计数器清零,同时所有的控制寄存器和状态寄存器及状态机都进行复位操作,且释放SCL和SDA总线为高电平;第三种,对主机的时钟低电平扩展累计时间tLOW:MEXT进行检测,在10ms内总线从START到ACK阶段、ACK阶段到下一个ACK阶段、ACK阶段到STOP的传输期间,一旦检测到主机在这3个阶段有字节传输之间或一个字节传输完毕后拉伸时钟低电平,就开始计数,该计数器一直累计,直到下一个阶段计数器清零,重新开始计数,一旦超过设置的超时阈值,见公式(5),则计数器清零,同时所有的控制寄存器和状态寄存器及状态机都进行复位操作,且在SCL和SDA总线上产生STOP条件。3.4SDA控制单元设计SDA控制单元控制I2C总线控制器的SDA总线。SDA控制单元设计时兼容了SMBus的设备地址分配识别和SMBus的PEC校验功能。3.4.1SMBus的设备地址SMBus设备地址类型可划分为很多种,如保留地址、目的性分配地址、动态分配地址等。这些地址的划分运用于不同协议层的特定场合或特定目的,详细说明参见SMBus协议规范及相关文献。当配置为SMBus设备时,在地址阶段通过地址匹配比较,识别SMBus的设备缺省地址0x1100001x;当配置为SMBus主机时,在地址阶段通过地址匹配比较,识别SMBus的Host地址0x0001100x。3.4.2SMBusPEC的产生和校验SMBus协议规范引进了数据包错误检测PEC机制来提高数据传输的可靠性,这个计算使用CRC-8多项式C(x)=x8+x2+x+1,对每一位串行数据进行计算得到。PEC是一个计算所有信息字节(包括地址以及读写位和数据字节)之后得到的CRC-8错误校验字节,该字节作为最后一个信息字节。当配置为SMBus发送设备,将地址字节以及读写位和数据字节的每一位进行串行CRC计算得到PEC字节,然后发送该字节;在PEC字节后接收到ACK响应表示这次写数据在从器件接收端被成功执行,否则收到NACK响应。当配置为SMBus接收设备,将地址字节以及读写位和数据字节的每一位进行串行CRC计算得到PEC字节,然后将接收的最后一个字节与该PEC字节进行比较,如果匹配则发送ACK响应,否则发送NACK响应。3.5状态机控制单元设计由于该控制器可以作为主机也可以作为从机,可作为发送器也可作为接收器,可作为I2C设备也可作为SMBus设备,为了兼容工作模式的多样性设计了状态机控制单元,该单元是I2C总线控制器的核心控制部分,主要负责实现I2C和SMBus的总线协议,控制I2C和SMBus工作模式选择及工作流程,产生读写时序及各状态标志。该单元由一个状态机控制实现,如图4所示,该状态机共有15个状态,具体描述见表4;状态之间的跳转及其跳转条件在表5中简要地进行了阐述。4仿真验证为确保该I2C总线控制器功能和时序的正确性、通信的稳定性以及与SMBus的兼容性,将该I2C控制器与I2C外设模型或SMBus外设模型连接[11],对该控制器进行了全面的仿真,使用的仿真器为Cadence公司的NC-Verilog。表4状态机状态描述状态名称状态描述IDLE空闲状态,设备默认模式是I2C从机接收模式START起始状态HEADER地址头字节状态,仅在10位地址模式时适用HEADER_ACK地址头字节响应状态,仅在10位地址模式时适用ADDRESS地址状态ADDRESS_ACK地址响应状态,从机模式进行地址匹配,主机模式等待响应TXDATA发送数据状态,DR的8位数据通过SR发送到总线TXDATA_ACK发送数据响应状态TXPEC发送校验状态,CRC计算的PEC字节通过SR发送到总线TXPEC_ACK发送校验响应状态RXDATA接收数据状态,总线接收的8位数据通过SR存储到DRRXDATA_ACK接收数据响应状态RXPEC接收校验状态,总线接收的PEC字节通过SR存储到DRRXPEC_ACK接收校验响应状态,接收的PEC字节与CRC计算的PEC字节进行校验STOP停止状态,传输结束图4I2C总线控制器状态机本文设计的I2C总线控制器支持I2C协议和SMBus协议,二者都有4种工作模式,分别为主机发送模式、主机接收模式、从机发送模式和从机接收模式;且都支持7位地址传输模式和标准模式;此外,作为I2C设备还支持10位地址传输模式和快速模式,作为SMBus设备还支持PEC传输和超时检测。针对I2C和SMBus的兼容性,同时结合不同的工作模式和时序分别仿真验证。表5状态机跳转条件编号跳转状态跳转条件1IDLE→START检测到START指令时进入主机模式;或检测到START起始条件时保持为从机模式2START→HEADER发送/接收10位地址模式的高两位(11110xx)地址及R/W位3START→ADDRESS发送/接收7位地址模式的地址及R/W位4HEADER→HEADER_ACK发送/接收完成8位HEADER字节5HEADER_ACK→ADDRESS发送/接收10位地址模式的低8位地址6ADDRESS→ADDRESS_ACK发送/接收完成8位ADDRESS字节7HEADER_ACK→TXDATAR/W位是“0”且DR中有待发送数据8ADDRESS_ACK→TXDATAR/W位是“0”,DR中有待发送数据且未满足条件19、229TXDATA→TXDATA_ACK发送完成8位DR字节10TXDATA_ACK→TXDATADR中有待发送数据且未满足条件20、2311HEADER_ACK→RXDATAR/W位是“1”且DR数据待接收12ADDRESS_ACK→RXDATAR/W位是“1”,DR数据待接收且未满足条件19、2213RXDATA→RXDATA_ACK接收完成8位DR字节14RXDATA_ACK→RXDATADR数据待接收且未满足条件21、2415TXDATA_ACK→TXPECPEC使能,PECR有待发送数据且未满足条件20、2316TXPEC→TXPEC_ACK发送完成8位PECR字节17RXDATA_ACK→RXPECPEC使能,PEC字节待接收且未满足条件21、2418RXPEC→RXPEC_ACK接收完成8位PECR字节19ADDRESS_ACK→START检测到START指令或检测到START起始条件20TXDATA_ACK→START检测到START指令或检测到START起始条件21RXDATA_ACK→START检测到START指令或检测到START起始条件22ADDRESS_ACK→STOP检测到STOP指令或检测到STOP起始条件23TXDATA_ACK→STOP检测到STOP指令或检测到STOP起始条件24RXDATA_ACK→STOP检测到STOP指令或检测到STOP起始条件25TXPEC_ACK→STOP发送PEC响应结束自动跳转26RXPEC_ACK→STOP接收PEC响应结束自动跳转27STOP→IDLE传输结束图5是对I2C总线控制器与I2C外设模型进行仿真,验证I2C总线控制器的快速400kHz模式和7位地址模式。将其配置为I2C主机发送模式,主时钟为36MHz,那么相应的I2C外设就工作在从机接收模式。从仿真图中看到,发送器DR的第一个数据是从机的7位设备地址和1位写标志,第二个和第三个数据是发送到从机的数据。此外,当DR为空且在下一个字节的ACK阶段MCU仍然没有写数据到DR,则此时SR也为空,即图中i2c_txe与i2c_btf同时为高时,SCL总线会持续保持低电平,直到MCU写数据到DR,同时SCL总线被释放为高电平,且SCL与SDA必须满足数据建立时间;仿真结果表明主机的发送数据与从机的接收数据一致。图5I2C快速模式、7位地址模式的仿真波形图6是对I2C总线控制器与I2C外设模型进行仿真,验证I2C总线控制器的标准100kHz模式和10位地址模式。将其配置为主机接收模式,主时钟为20MHz,主机DR的第一个数据是从机的10位设备地址的Header地址和1位写标志(11110100),第二个数据是从机的10位设备地址的Address地址(10010010),所以发送的从机10位设备地址是0x292;因为配置为接收模式,重新发送START和Header,同时改变传输方向为读标志(11110101),工作流程见图4;此外,i2c_rxne标志为高时表示一个字节接收完毕,等待MCU读取数据,一旦MCU完成读DR操作,该标志就硬件自动清除。图6I2C标准模式、10位地址模式的仿真波形图7是对I2C总线控制器与SMBus外设模型进行仿真,验证SMBus的PEC功能。将其配置为SMBus工作速度10kHz,7位地址模式,主时钟为8MHz;仿真中主机和从机都使能了PEC功能,从地址字节以及读写位开始进行串行CRC计算,计算得到的字节就是本字节的校验结果,将其存入PECR,再接着对数据字节的每一位进行串行CRC计算,计算得到的字节就是前面所有信息字节的校验结果,将其更新到PECR,依次计算得到最后的校验结果,存入PECR,同时发送器将PECR作为最后一个字节发送到SDA总线,而接收器将最后一个字节接收存入DR,同时与接收器的PECR进行比较,从仿真结果判断二者的数据是一致的。图7SMBus工作速度10kHz、7位地址模式、带PEC校验的仿真波形图8是对I2C总线控制器与SMBus外设模型进行仿真,验证SMBus的超时检测功能。将其配置为SMBus工作速度100kHz,7位地址模式,主时钟为8MHz,根据公式(5)配置I2C_timeoutr为0x13880;从仿真图中看到,主机在地址响应阶段,MCU没有写入数据到DR,硬件一直保持SCL低电平,发生时钟拉伸现象,当累积时钟拉伸超时计数器计数到0x13880时,主机发生时钟低电平扩展累计时间超时,那么I2C_timeout标志置高,同时硬件自动产生一个STOP条件,传输结束。图8SMBus工作速度100kHz、7位地址模式、超时检测的仿真波形本设计在功能仿真正确之后,进一步确定其可实现性和时序满足性。利用Synopsys公司的综合工具DesignCompiler,在0.11μmeFlash工艺下对本设计进行综合,得到如下性能:门数约4571,动态功耗为0.0137mW/MHz,同时对综合网表也进行了全面的验证。5结论本文实现了一种片上兼容SMBus协议的I2C总线控制器的设计,该设计基于APB总线,采用模块化设计,层次分明,编写的VerilogHDL代码是可综合的,且与目前SOC系统中广泛使用的AMBA总线系统具有良好的兼容性;该控制器有多种工作模式,同时支持I2C和SMBus的通信格式和通信时序,在节省硬件资源的同时还节省了芯片管脚资源;最后,通过仿真验证了该控制器的总线通信稳定性。参考文献:【相关文献】[1]PhilipsSemiconductor.TheI2C-BusSpecification[Z].2000.[2]杨帆.基于I2C接口EEPROM读写控制器设计[J].微型机与应用,2015,34(10):22-24.[3]路铁生.系统管理总线(SMBus)与智能充电[J].电源世界,2011(8):36-39.[4]何国锋,刘宇红.基于SMBus协议的电池信息监测系统[J].电子技术应用,2016,42(4):49-52.[5]王炳文,段小虎,张婷婷.基于可编程逻辑的I2C总线控制器设计及应用[J].工业控制计算机,2017,30(5):21-22.[6]张文梅,刘伟,祩越强.基于Verilog的I2C控制器的设计与综合[J].电子设计工程,2011,19(19):116-119.[7]宋杰,陈岚,冯燕.一种I2C总线控制器的接口设计[J].信息与电子工程,2010,8(4):467-470.[8]胡春媚,蒋永花,郭阳.支持多种模式传输的I2C控制器设计[J].微电子学与计算机,2010,27(9):117-121.[9]陈涛,万亚坤.基于智能电池系统的SMBus总线研究及IP设计[J].中国集成电路,2008(11),48-51.[10]SBSImplementersForum.SystemManagementBusSpecificationVersion2.0[S].2000-8-3:1-35.[11]沈圣盛.基于APB总线的接口IP核设计与验证[D].西安:西安电子科技大学,2011.',)

提供一种兼容SMBus协议的I2C总线控制器的设计会员下载,编号:1700666162,格式为 docx,文件大小为10页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载