Aurora接口使用说明,word接口使用说明

本作品内容为Aurora接口使用说明,格式为 docx ,大小 2319434 KB ,页数为 12页

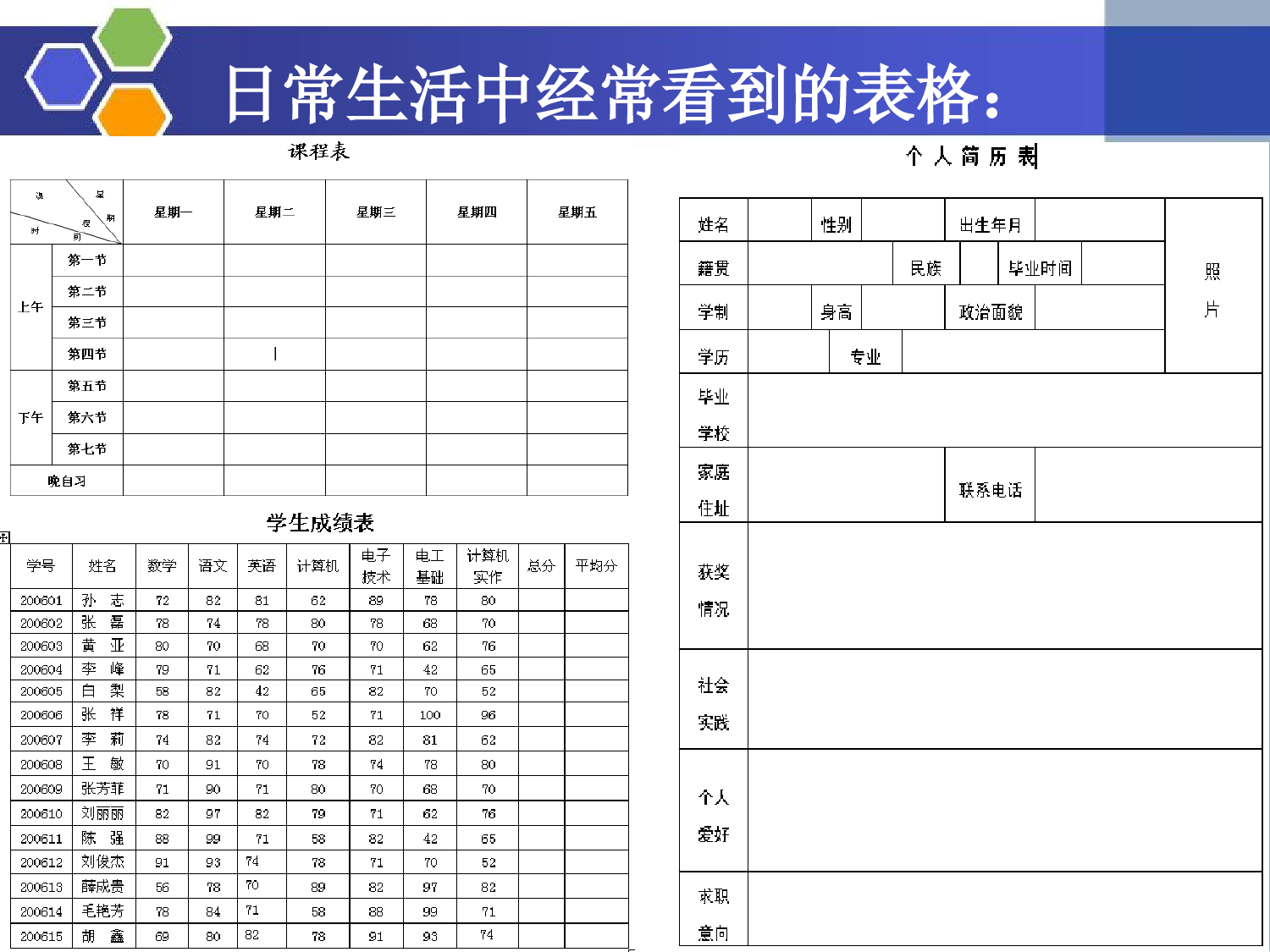

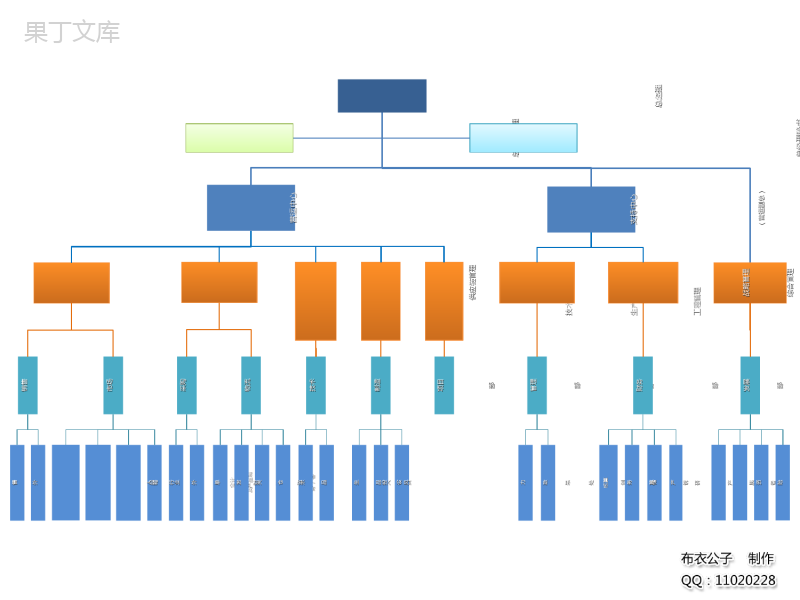

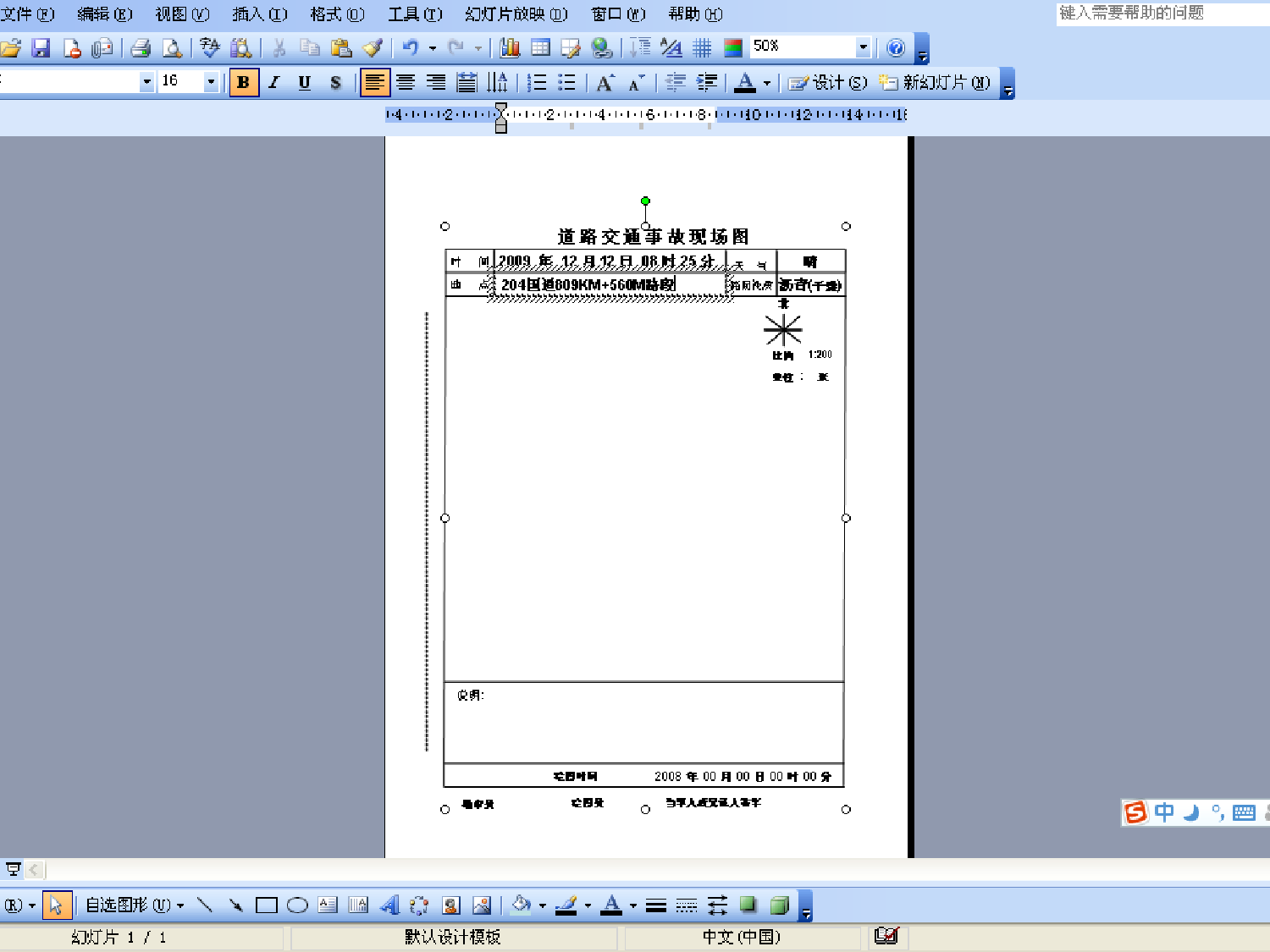

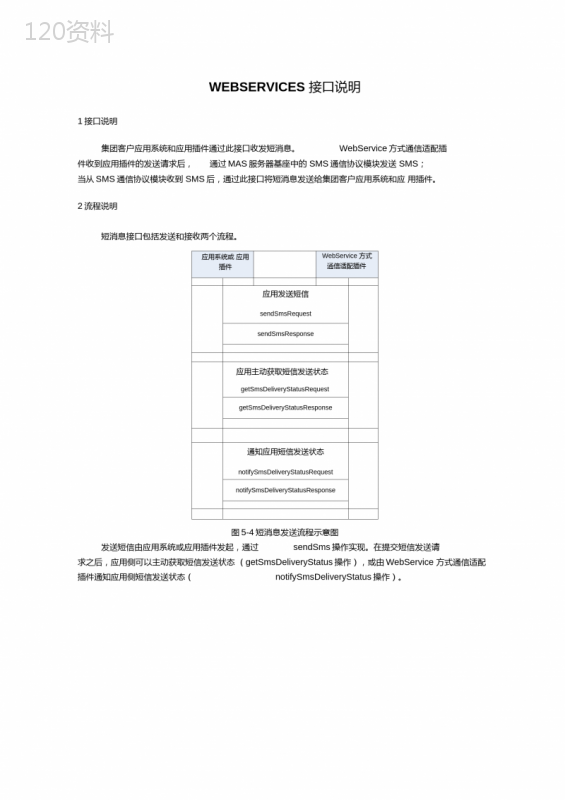

('word格式-可编辑-感谢下载支持在AMC-2C667X平台上使用FPGA的Aurora接口说明声明:本文档仅面向初学者。1、针对平台用的V6芯片型号新建一个ISE工程,工程中加入AuroraIP核,IP核的设置如下(当然也可以选择其他设置,以下均是针对本测试设置而言)图1主要参数:lanes-通道数,即使用的GTX收发器个数Lanewidth:aurora核与用户接口的数据位宽(一般可选2B或者4B)Lanerate:Aurora核的对外通信速率,由于采用8B/10B编码,实际有效速率要乘以0.8。GTREFCLK:GTX参考时钟频率采用全双工,流水通信模式。详细请参考Aurora的UG。好了,最后一页了,这IP核设置够简单吧!!!(一共才两页好伐…),让你选择GTX位置图2平台上的V6片子一共有6组GTXQUAD,每个QUAD有4个GTX,选择一个GTX与平台word格式-可编辑-感谢下载支持的SFP+F2相连,平台说明书写清楚了,是MGT_113_1,就是它了。生成了这个核以后,核的文件夹下会多出一堆文件,这就是XILINX给你的一个示例工程-exampledesign.图3接下来就可以仿真啦。仿真:你可以直接使用它提供的testbench仿真,没问题。但是有更简单的方法,其实你仿真只是为了看看它的时序,看看你加的东西对不对,因为只要你加对了,仿真一定通过。那么简单的方法呢?打开modelsim,不要告诉我你没装,或者装了没有关联ISE仿真库,那你得先把这个问题解决了再说。好了之后,新建一个modelsim工程(file-new…)在你之前那堆文件的/simulation/functional文件夹下,看图说话~图4下一个界面叫你createnewfiles啥的直接close。然后你就在modelsim命令窗口轻轻地敲了一行命令:dosimulate_mti.do这个simulate_mti.do就是人家已经仿真好的仿真文件,就在那个文件夹里,意思就是我仿好了,你拿去用吧,看看就好,没什么技术含量。Soitbegins:word格式-可编辑-感谢下载支持图5当然敲了这个命令你的modelsim可能会报错,多半是因为XILINX环境变量的设置问题,去百度找下答案。编译通过了之后过了一会,就出现了这个界面:图5请务必点否,否则你百忙了…然后如果出现了最终的仿真波形,那么恭喜你成功了!!word格式-可编辑-感谢下载支持图6当然你也可以让仿真多持续一段时间,怎么弄呢?你需要自己去改它的testbench。作为一个使用快速使用该IP的文档,我只告诉你我们需要关注的信号无非这么几个,下图中黑的信号:图7简单吧!上面的五个信号就是用户接口信号,下面的几个是系统接口信号,你要做的就是写个模块产生数据然后送到Aurora核当中,所以请重点关注那几个用户接口信号及其时序。这几个信号什么意思怎么用?参考UG。________________________________华丽丽的分割线_____________________________2、接下来是重点,请至少先读了下Aurora的UserGuide。综合实现:下面你要做的就是,针对它重新新建一个工程,然后把那堆文件夹内的所有.v(hd)和.ucf文件都包含就去,结果就是一个可编译的可用的东西,这些东西没看懂?其实我也没看懂,没关系。当然有些地方你需要改动,慢慢往下看。word格式-可编辑-感谢下载支持这个工程建立以后就是这样的:图8当然,chipscope的那几个核是我手动添加的方便查看信号而已,你要是牛逼,能直接保证对就不用加了。要使用那几个核,上图右侧有个参数叫USE_CHIPSCOPE要设置为1。接下来看看这个工程的大体结构:Aurora_module_i:以源代码的形式给了你Aurora核的实现,与在这里直接添加一个AuroraIP核一样一样的…是为了方便你修改其中的某些参数。如果不是大神,请不要肆意修改它。Standard_cc_module_i:时钟补偿模块,用来给通信双方进行时钟补偿,因为这个协议对时钟要求很高,两端的时钟频偏在100个ppm内都可以补偿回来,时钟同步嘛~Frame_gen_i/frame_check_i:用户接口端程序,你要写用户程序可以参考它对Aurora用户接口的操作方式,其实很简单,UG里面有一个用户接口时序。其他的不说了自己看吧。然后你就需要考虑修改ucf文件了,要针对你的片子和平台,这个一开始不熟的话有点头痛的…下面是我跑通的ucf,给你的参考价值只在于它的管脚锁定:##UCFgeneratedforxc6vlx240t-ff1759-2device###125.0MHzGTXReferenceclockconstraintNET"GTXQ1_left_i"TNM_NET=GT_REFCLK;TIMESPECTS_GTXQ1_LEFT_I=PERIOD"GT_REFCLK"125.0MHzHIGH50%;#UserClockConstraint:basedonthelinerate(2.0Gbps)andlanewidth(2-Byte)NET"user_clk_i"TNM_NET=USER_CLK;TIMESPECTS_USER_CLK_I=PERIOD"USER_CLK"100.0MHzHIGH50%;#MGT113REFCLK1NETGTXQ1_PLOC=AD8IOSTANDARD=LVDS_25DIFF_TERM=TRUEPERIOD=8nsPRIORITY0;NET"GTXQ1_N"DIFF_TERM="TRUE";NET"GTXQ1_N"IOSTANDARD=LVDS_25;NET"GTXQ1_N"LOC=AD7;word格式-可编辑-感谢下载支持#DiffINITClockConstraint#RefClocksforFPGA1-100M//mustlowerthanrefclkofGTXNET"INIT_CLK_P"DIFF_TERM="TRUE";NET"INIT_CLK_P"PERIOD=10ns;NET"INIT_CLK_P"IOSTANDARD=LVDS_25;NET"INIT_CLK_P"LOC=J42;NET"INIT_CLK_N"DIFF_TERM="TRUE";NET"INIT_CLK_N"IOSTANDARD=LVDS_25;NET"INIT_CLK_N"LOC=K42;#100MHzboardClockConstraintNET"reset_logic_i/init_clk_i"TNM_NET=INIT_CLK;TIMESPECTS_INIT_CLK=PERIOD"INIT_CLK"10nsHIGH50%;TIMESPEC"TS_TIG1"=FROM"INIT_CLK"TO"USER_CLK"TIG;NETGT_RESET_INLOC=AD31;//NETRESETPULLUP;//NET"RESET"LOC=P28;//NETLEDLOC=N28;#ErrorsIndicatorsNETHARD_ERRLOC=N28;#LED2_FPGA0NETSOFT_ERRLOC=P28;#LED3#ChannelandLaneupIndicatorsNETCHANNEL_UPLOC=K33;#LED0NETLANE_UPLOC=K32;#LED1//NETclk_dis_outLOC=L32;#LED7#GTLocation-MGT_113_1INSTaurora_module_i/gtx_wrapper_i/GTXE1_INST/gtxe1_iLOC=GTXE1_X0Y5;#TX/RXlocationNETRXPLOC=AF3;#MGT_113_1,connectedtoSFP+F2NETRXNLOC=AF4;NETTXPLOC=AJ1;NETTXNLOC=AJ2;很好很强大有木有!!我当时调这个的时候就没个人直接给我个ucf…然后程序中还有些地方需要改动,慢慢往下看。看见ucf文件中关于复位的部分没有?就是这段:NETGT_RESET_INLOC=AD31;//NETRESETPULLUP;//NET"RESET"LOC=P28;//NET"GT_RESET_IN"LOC=N28;注释的部分就是它原本生成的东西,把两个复位信号RESET和GT_RESET_IN分别约束到两个按键上来复位,这个复位按照UG上的说明还有一定的时序要求,但是一般这样约束都不会有问题,比如XILINX官word格式-可编辑-感谢下载支持方板子这样约束是没问题的。但是我们的平台就不行了,为什么?因为没有按键!它不是个开发板啊……然后我尝试过另外的复位方法:写个小程序定时复位,还有就是通过chipscope的虚拟IO口核VIO给Aurora施加复位信号,均无果而终。那么为什么要把GT_RESET_IN约束到AD31那个管脚上呢?首先解释下我是这样弄的:wireF1_F0_WARM_RESET;assignF1_F0_WARM_RESET=!GT_RESET_IN;aurora_125m_RESET_LOGICreset_logic_i(.RESET(F1_F0_WARM_RESET),.USER_CLK(user_clk_i),.INIT_CLK_P(INIT_CLK_P),.INIT_CLK_N(INIT_CLK_N),.GT_RESET_IN(F1_F0_WARM_RESET),.TX_LOCK_IN(tx_lock_i),.PLL_NOT_LOCKED(pll_not_locked_i),.SYSTEM_RESET(system_reset_i),.GT_RESET_OUT(gt_reset_i));也就是说,把reset_logic这个模块(为啥是它?因为它的作用就是对输入的复位信号进行时钟去抖和时序纠正然后把输出的复位供给其他模块使用)的两个复位信号—RESET和GT_RESET_IN连到了同一根信号上,即F1_F0_WARM_RESET,而它是连接到AD31管脚连接进来的复位信号的取反信号上。AD31这个管脚连接到了平台上FPGA1给FPGA0热复位的信号上,因此它连接的是一个复位信号,而取反只是为了将低有效转为高有效而已,因为Aurora中的模块都是用高电平有效复位。就这么一个复位问题,不知道耗了我多少宝贵时间啊~复位的问题解决了,时钟呢?约束文件中有这么几段:#125.0MHzGTXReferenceclockconstraintNET"GTXQ1_left_i"TNM_NET=GT_REFCLK;TIMESPECTS_GTXQ1_LEFT_I=PERIOD"GT_REFCLK"125.0MHzHIGH50%;#UserClockConstraint:basedonthelinerate(2.0Gbps)andlanewidth(2-Byte)NET"user_clk_i"TNM_NET=USER_CLK;TIMESPECTS_USER_CLK_I=PERIOD"USER_CLK"100.0MHzHIGH50%;#MGT113REFCLK1NETGTXQ1_PLOC=AD8IOSTANDARD=LVDS_25DIFF_TERM=TRUEPERIOD=8nsPRIORITY0;NET"GTXQ1_N"DIFF_TERM="TRUE";NET"GTXQ1_N"IOSTANDARD=LVDS_25;NET"GTXQ1_N"LOC=AD7;#DiffINITClockConstraint#RefClocksforFPGA1-100M//mustlowerthanrefclkofGTXNET"INIT_CLK_P"DIFF_TERM="TRUE";NET"INIT_CLK_P"PERIOD=10ns;NET"INIT_CLK_P"IOSTANDARD=LVDS_25;NET"INIT_CLK_P"LOC=J42;word格式-可编辑-感谢下载支持NET"INIT_CLK_N"DIFF_TERM="TRUE";NET"INIT_CLK_N"IOSTANDARD=LVDS_25;NET"INIT_CLK_N"LOC=K42;主要是Aurora中GTX时钟和user_clk的约束问题,如果你不清楚这两个时钟是啥?要不留一页篇幅等你看看UG?算了,继续吧还是~哈哈平台中FPGA0的可用外部时钟资源有好几个,来来截个图看看:图9第一到第三个时钟质量一般,啥叫质量一般?就是它的精度、稳定度和抖动达不到Aurora对时钟的要求。但作一般的逻辑使用的时钟足够了。请注意,AuroraUG中说得很明确,它对时钟要求还是很高的,所以别耍什么花样,不然传输数据出现丢包,错误啥的就只能怪你自己了,虽然能够进行时钟补偿,但是100ppm范围有限。后面的几个时钟,你应该注意到了-lowjitter.质量相对较高,尤其是从CDCE62005出来的那两个,可是GPS同步时钟啊亲~~基于对联要求,我选择的是那个125M的lowjitter时钟,实际上,对应于一个线速度,在Aurora核的界面出来的几个可选时钟都是可以的,甚至你生成核以后再修改时钟约束都行,只要是这个线速度对应的时钟列表里的时钟范围,亲测有效。关于平台上时钟与GTX的连接,来个壮观点的图表:word格式-可编辑-感谢下载支持图10由于平台中的SFP+F2连接的是MGT_113_port1那个GTX,因此时钟就选择REFCLK_113_CLK1,这个时钟驱动本QUAD和相邻QUAD的GTX都没问题。它在V6的管脚对应位置为AD8/AD7。至于那个uer_clk的约束,就选择的是第一个普通的时钟,因为它是用来驱动用户逻辑的,不需要太高的质量。这里大部分工作就完成了,是不是很简单?当你熟了之后觉得确实很简单,但是它却花了你较长的时间去熟悉…word格式-可编辑-感谢下载支持----------------------------------空几行留你思考下--------------------------------这时候你就可以进行测试了-先自环再平台对联。自环的话,可以是光纤自环,用一根光纤把SFP+F2(最下面那个SFP+,一共有三个噻)模块的收发端短接起来。另一种自环就是近端PMA/PCS自环(参见v6_GTXuserguide),目的是为了检验GTX是否工作正常。正常情况下,这两种自环是能通的,而且因为是时钟同源时钟,收发两端不存在时钟频差,因此也不涉及时钟补偿问题。但是呢……我们这个平台光纤自环是不能通的,必须进行更多的时钟补偿,要修改时钟补偿模块(囧)。怎么修改呢?其实这应该是你的事,修改程序嘛,不过我还是简单说说吧。图11在ISE中打开时钟补偿模块,你要做的就是修改下count_24d_srl_r和count_24d_flop_r两个变量的字长如上图中的注释reg部分,名字都可以不用改。然后找到与这两个变量相关的两端程序:word格式-可编辑-感谢下载支持把其对应的字长和循环移位的长度改一下就好了。修改这段大概是啥子意思呢?意思就是更加频繁地增加时钟补偿,不细说了。然后就大功告成了,光纤自环包括后面的平台对联(对联的时候请记住两个平台上的程序均使用一样的时钟补偿)都能成功了。自环和对联时用chipscope抓取的信号图就是下面两位:图12图13对联的模式就是酱式儿的:word格式-可编辑-感谢下载支持图14忘了一点,Aurora建链的时候一定是要插光纤的,不插就会初始化失败,光纤自环你可以插拔下光纤试试,那两个建链指示灯都是会变的。判断成没成功的关键就是chipscope中channel_up和lane_up对应的两个信号是不是稳定拉高,不出现不时拉低的情况,如果是,那么恭喜你又成功了,就可以用它了。(所以说XILINX的这些接口还是很强大的,尤其是其GTX)。哦,第二张chipscope图的user_clk一直是高电平并没错,因为我当时是用这个时钟采它自己。至于用户接口的数据,你自己可以用线性反馈移位寄存器产生随机数测试,是没问题的。OK,就酱了,其他的自己发掘吧。------------------------------------------------copyrightLBC-UESTC----------------------------------------------------',)

提供Aurora接口使用说明,word接口使用说明会员下载,编号:1700773881,格式为 docx,文件大小为12页,请使用软件:wps,office word 进行编辑,PPT模板中文字,图片,动画效果均可修改,PPT模板下载后图片无水印,更多精品PPT素材下载尽在某某PPT网。所有作品均是用户自行上传分享并拥有版权或使用权,仅供网友学习交流,未经上传用户书面授权,请勿作他用。若您的权利被侵害,请联系963098962@qq.com进行删除处理。

下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载 下载

下载